点击蓝字 关注我们

全文刊载于《前瞻科技》2022年第3期"集成电路科学与工程专刊”,点击文末“阅读原文”获取全文。

曹立强

-研究员

-博士研究生导师

-中国科学院微电子研究所副所长

侯峰泽(通信作者)

-副研究员

近年来,先进封装技术的内驱力已从高端智能手机领域演变为高性能计算和人工智能等领域,涉及高性能处理器、存储器、人工智能训练和推理等。当前集成电路的发展受“四堵墙”(“存储墙”“面积墙”“功耗墙”和“功能墙”)制约,以芯粒(Chiplet)异质集成为核心的先进封装技术,将成为集成电路发展的关键路径和突破口。文章概述近年来国际上具有“里程碑”意义的先进封装技术,阐述中国大陆先进封装领域发展的现状与优势,分析中国大陆先进封装关键技术与世界先进水平的差距,最后对未来中国大陆先进封装发展提出建议。

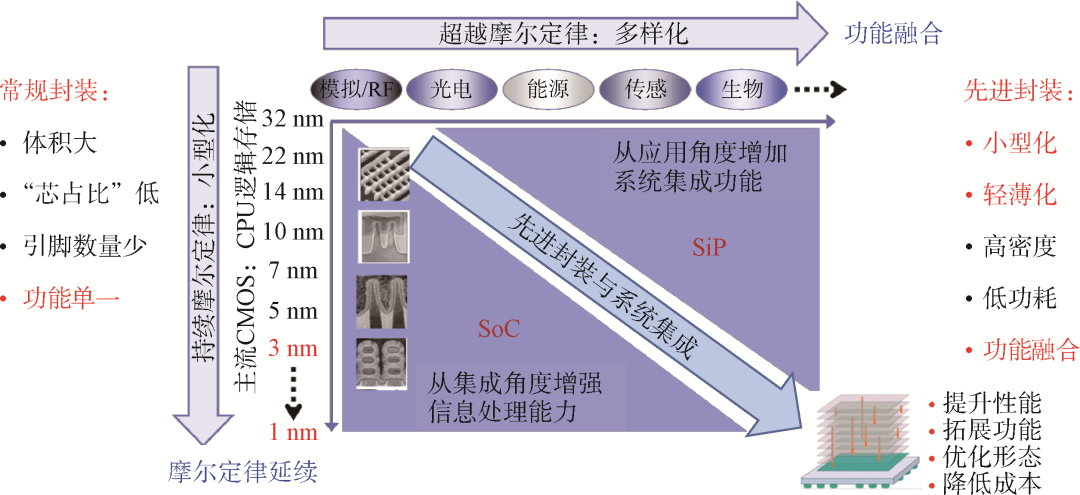

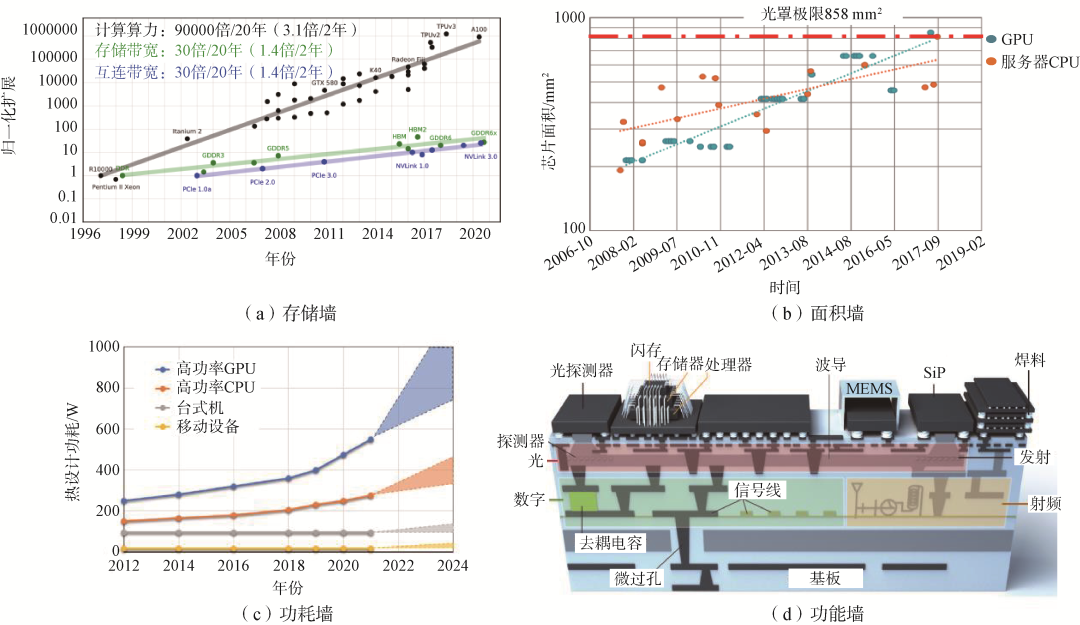

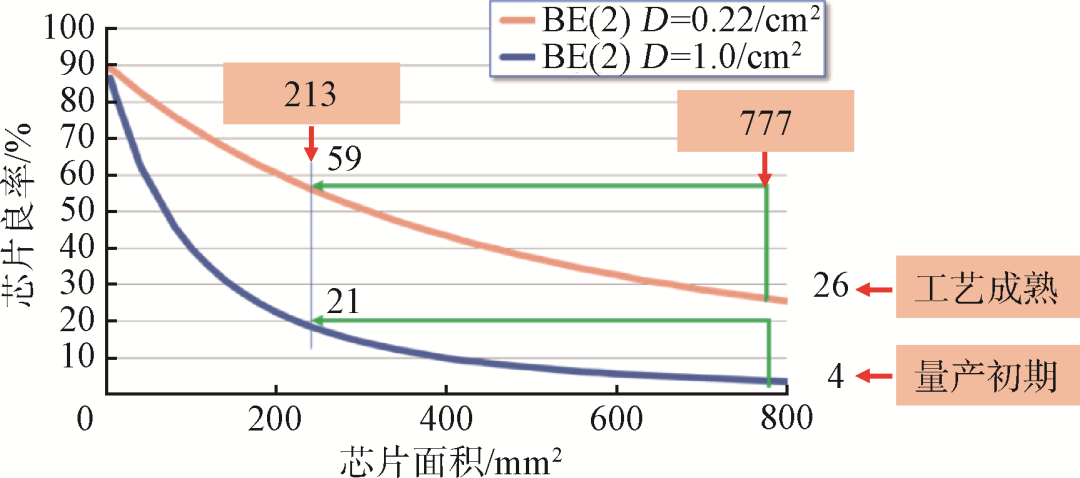

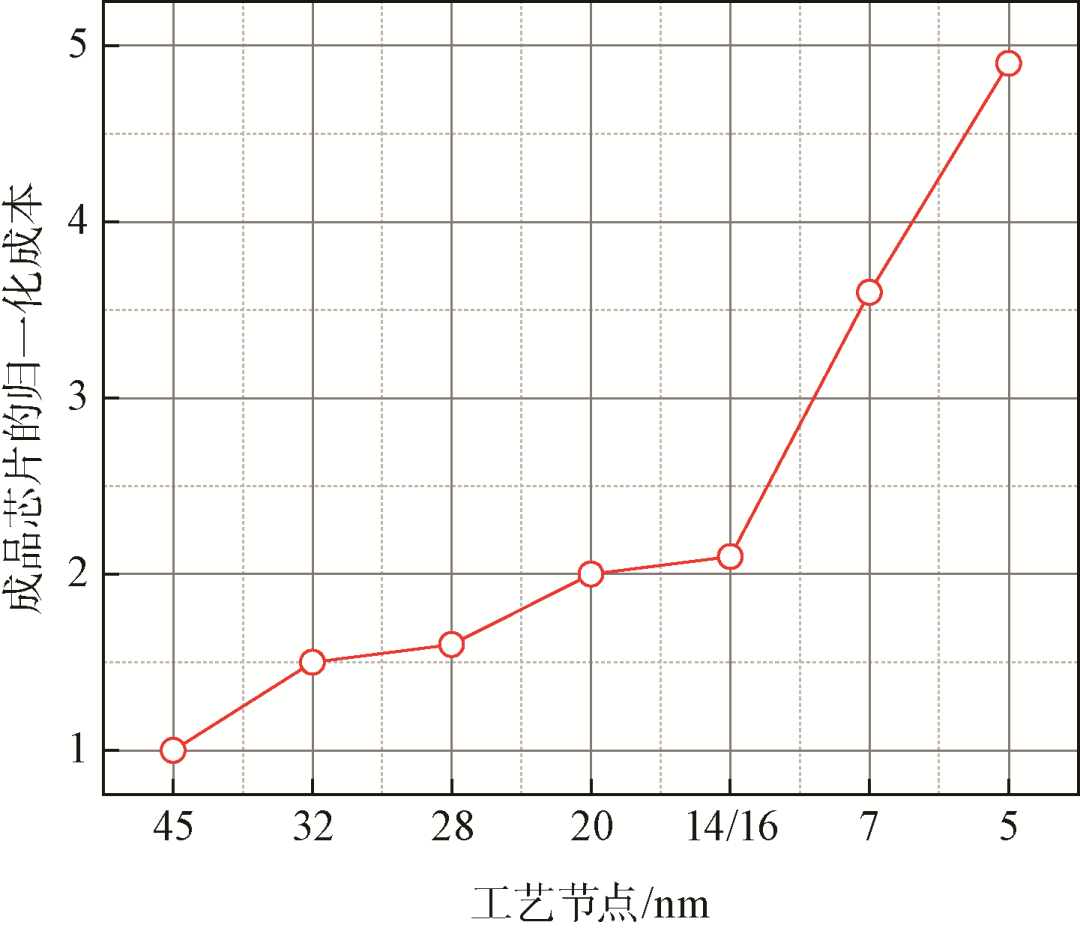

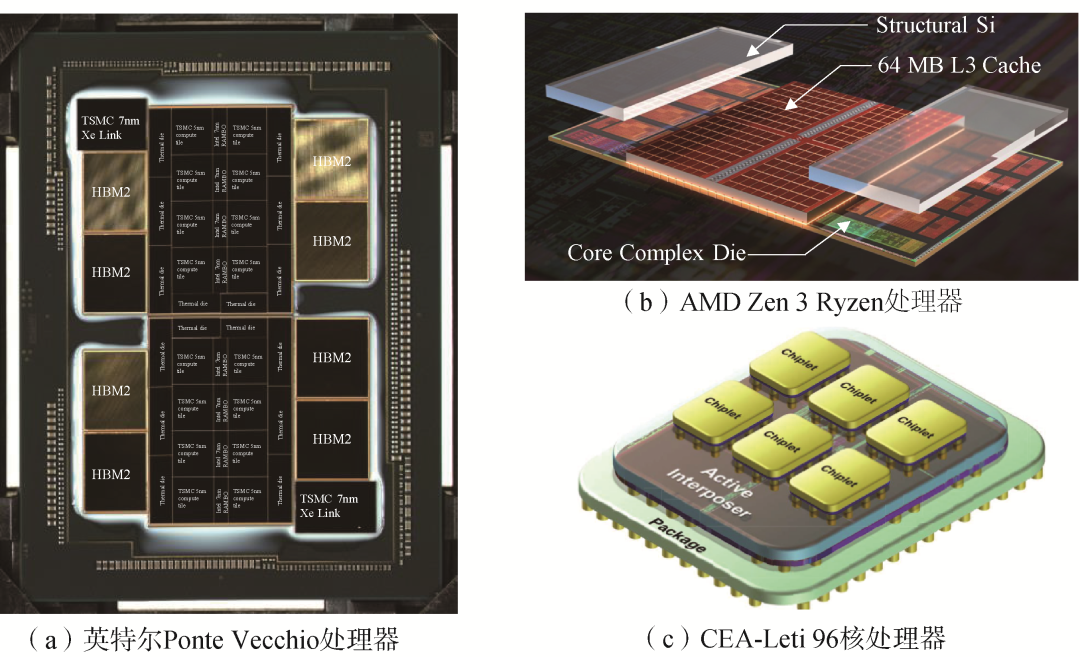

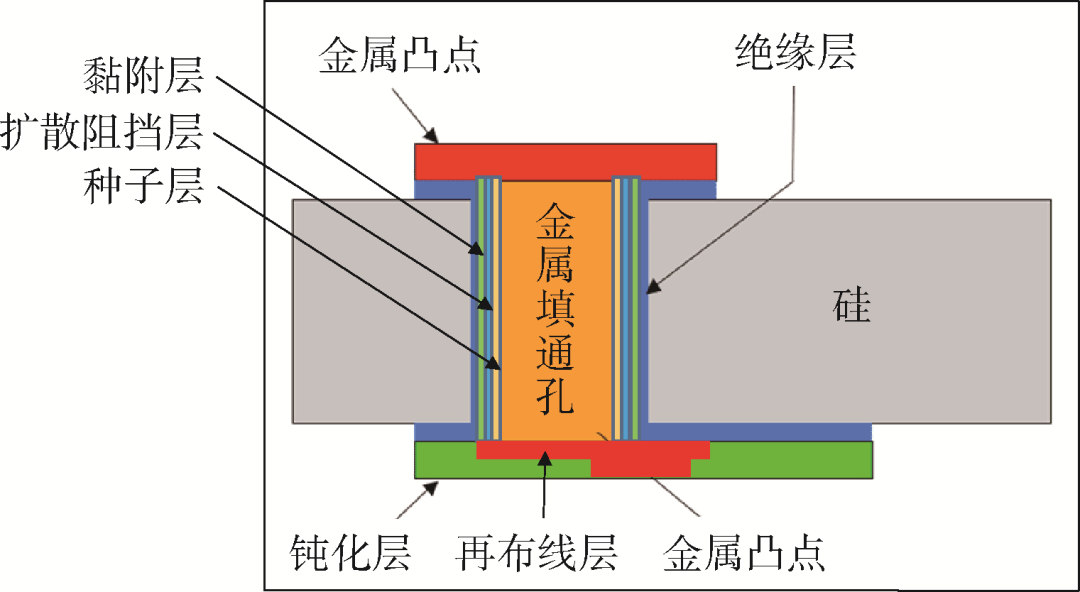

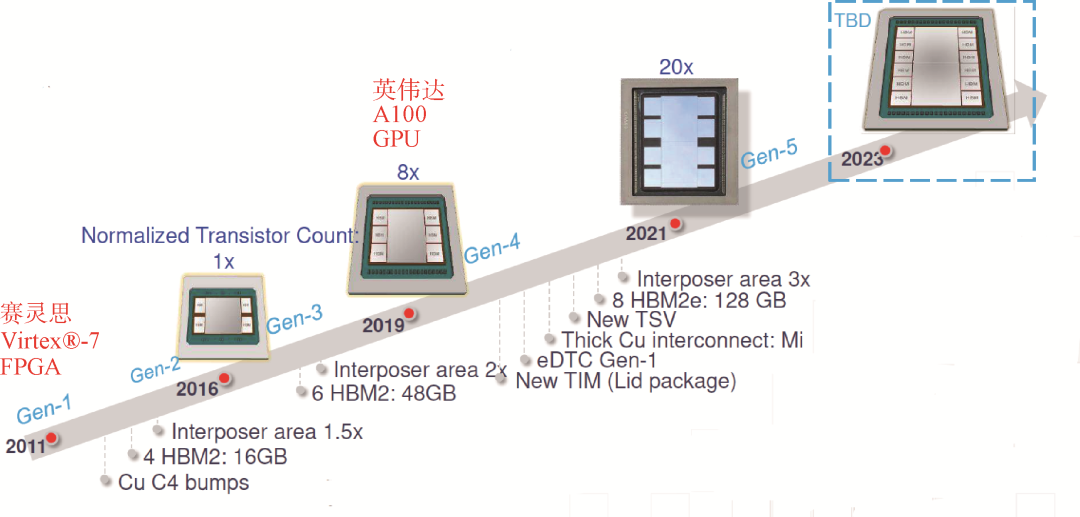

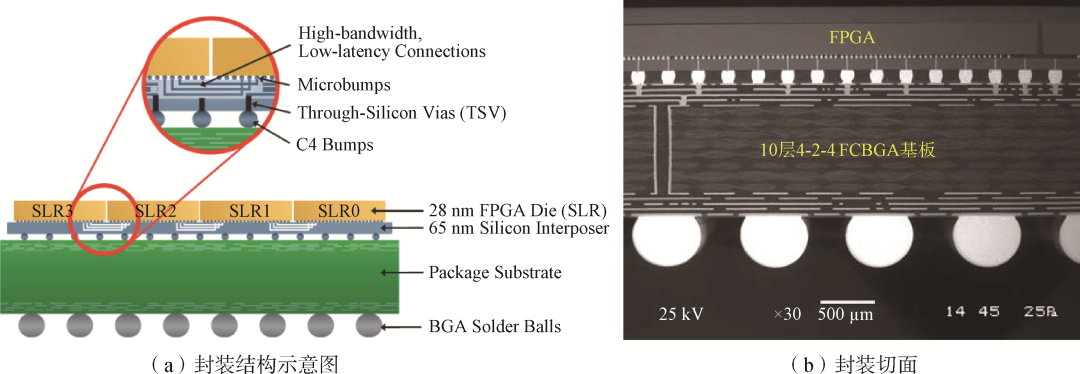

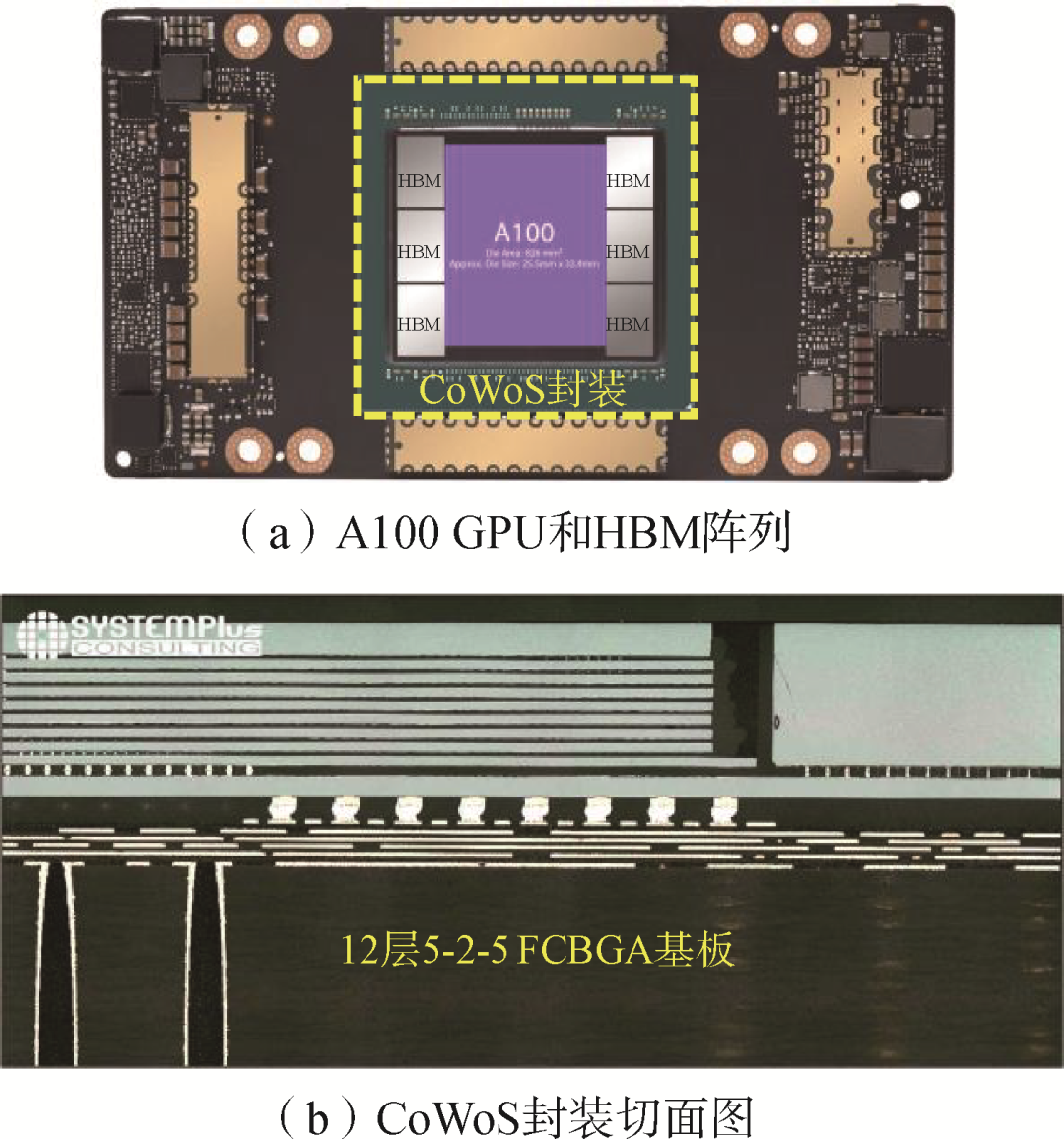

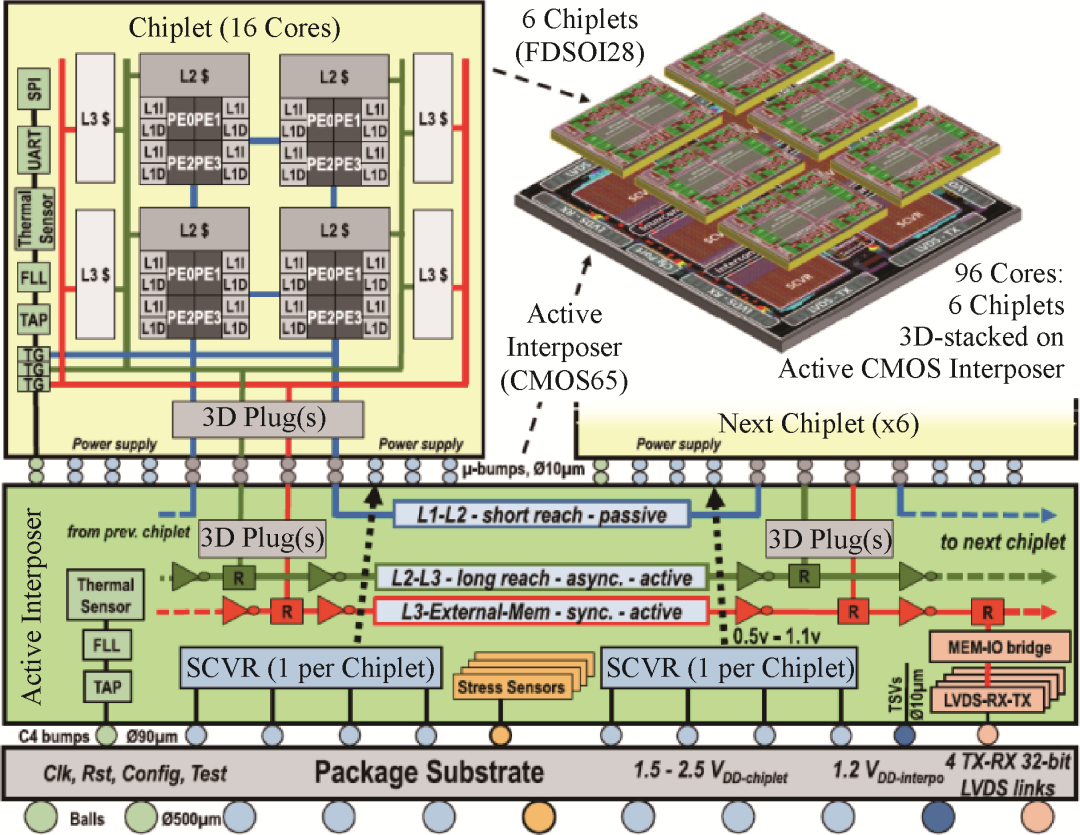

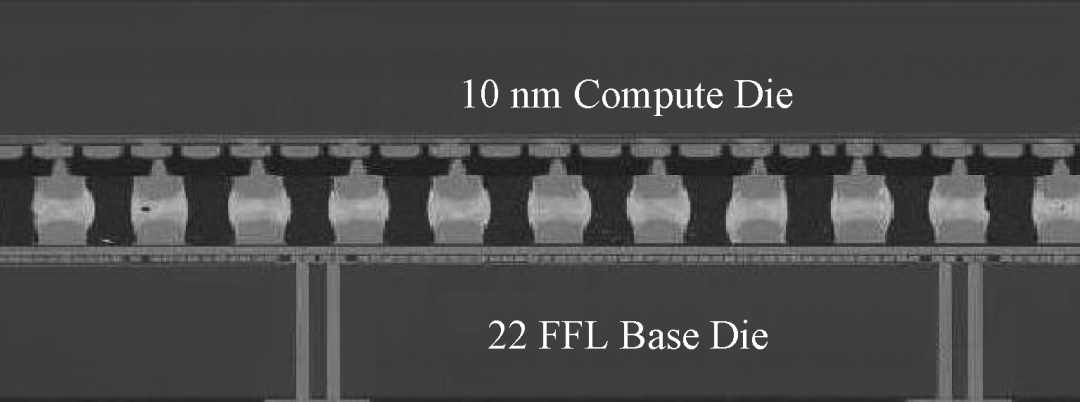

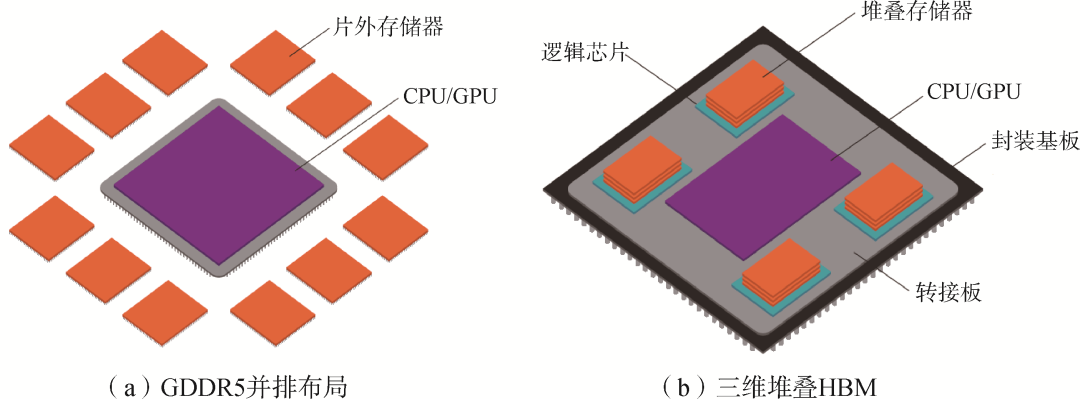

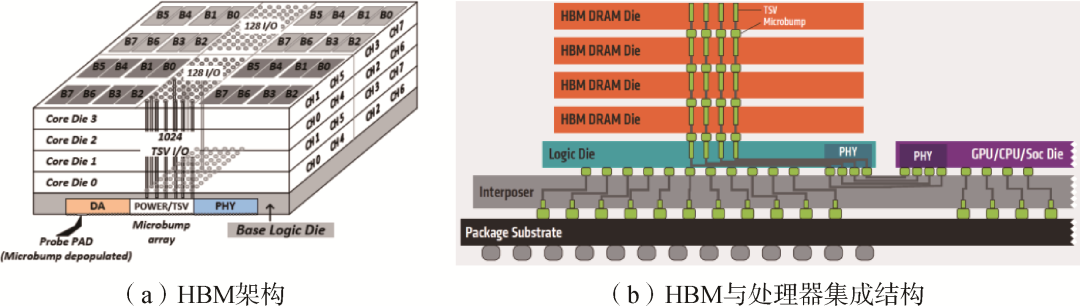

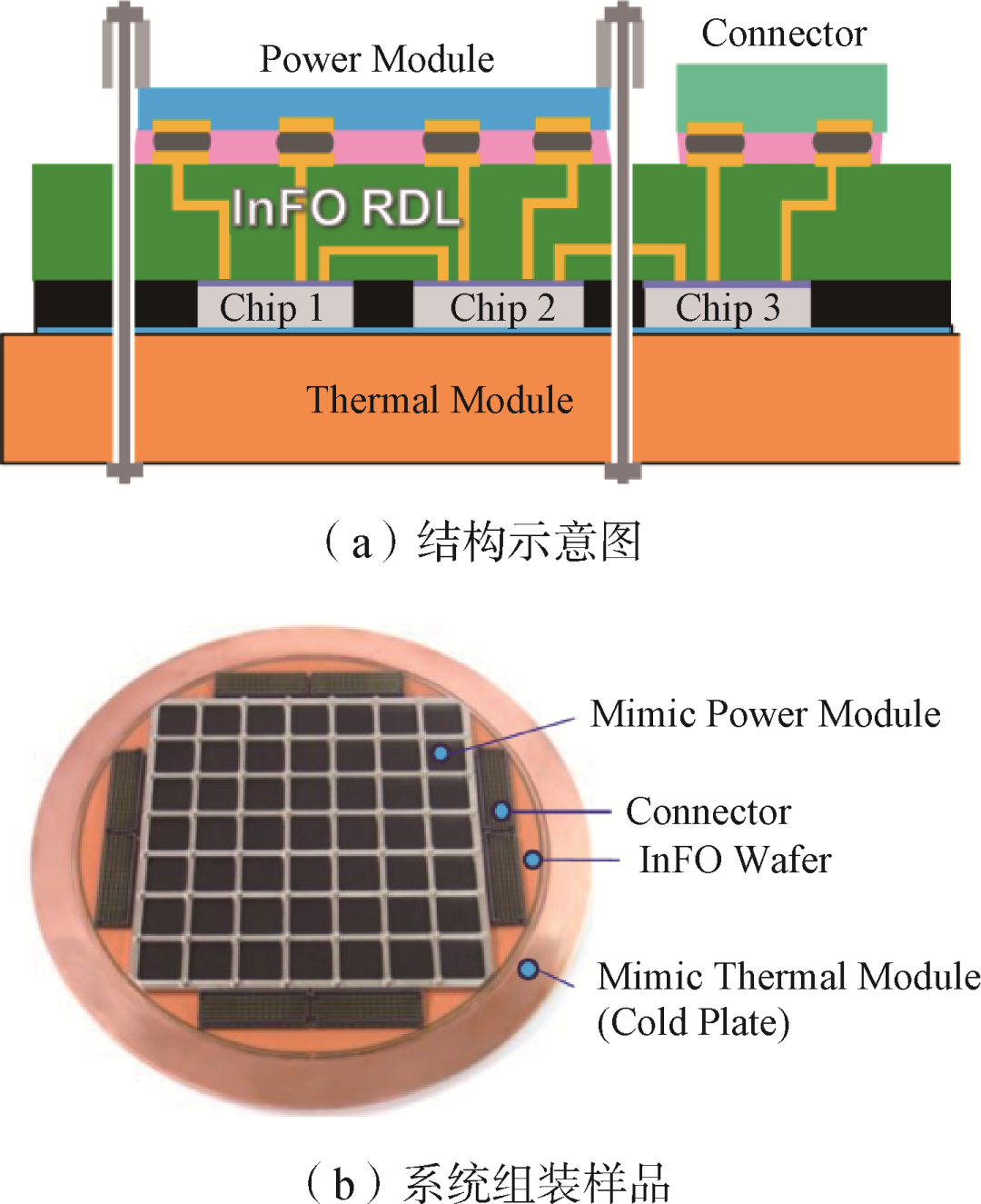

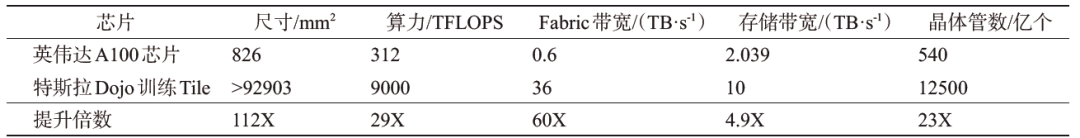

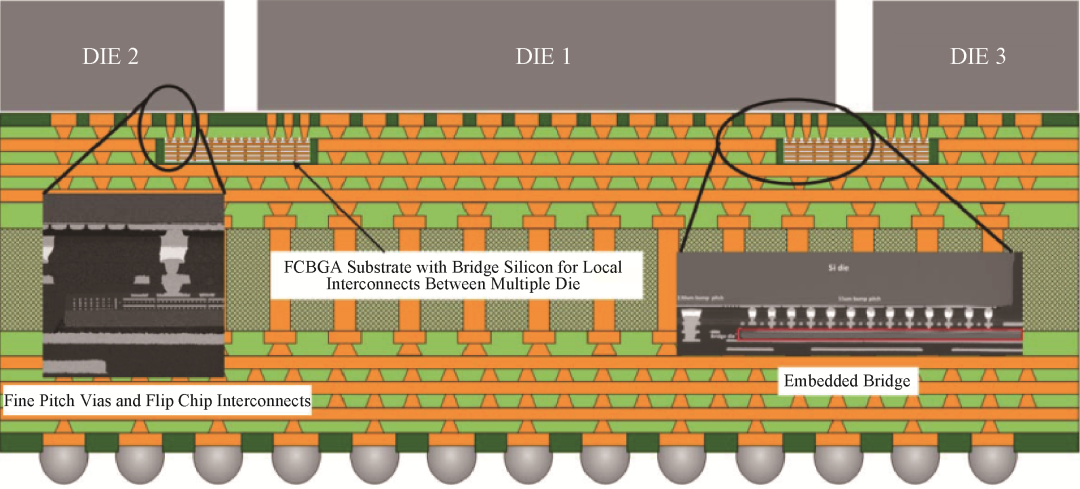

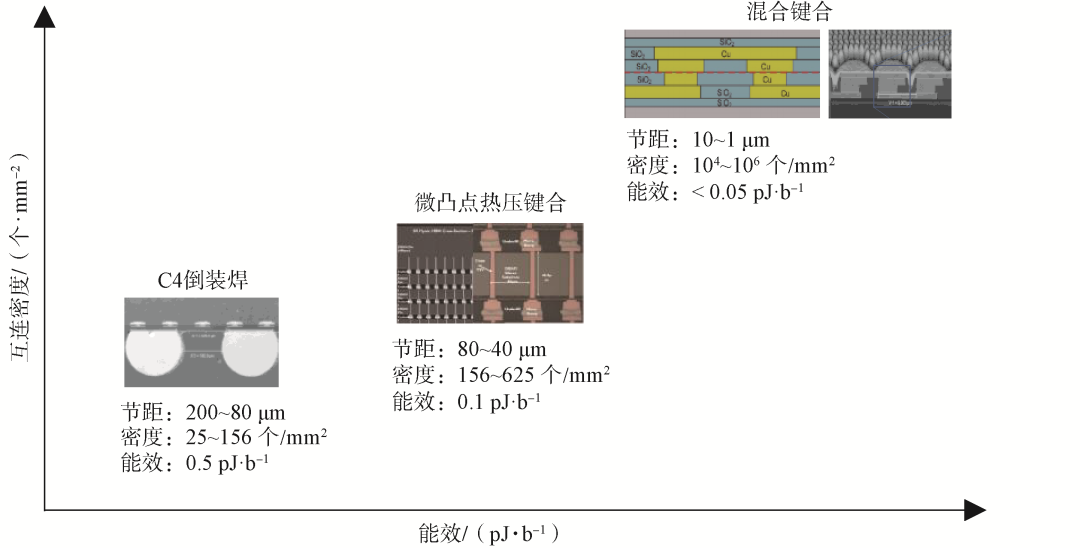

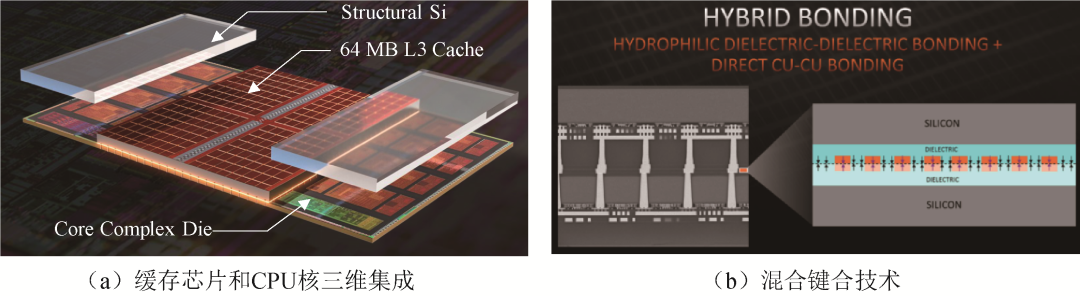

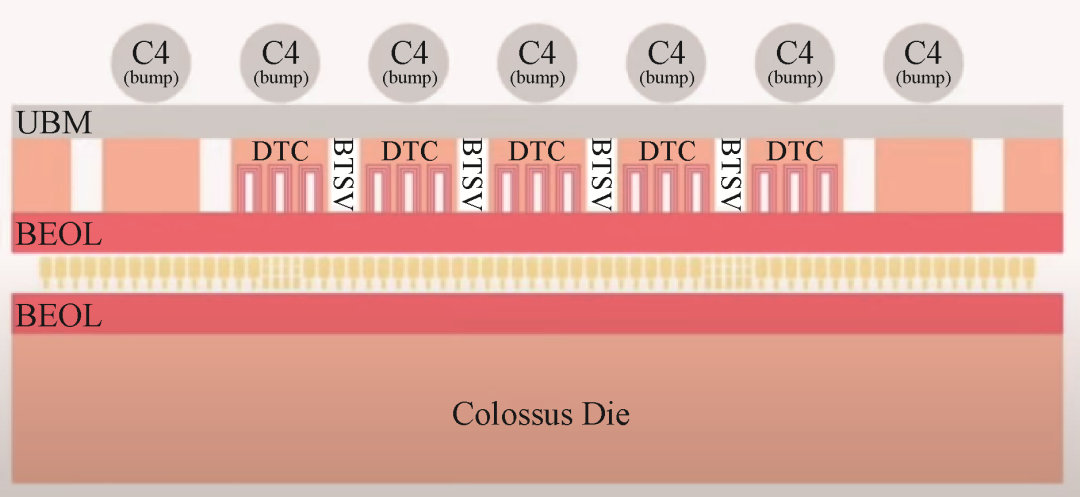

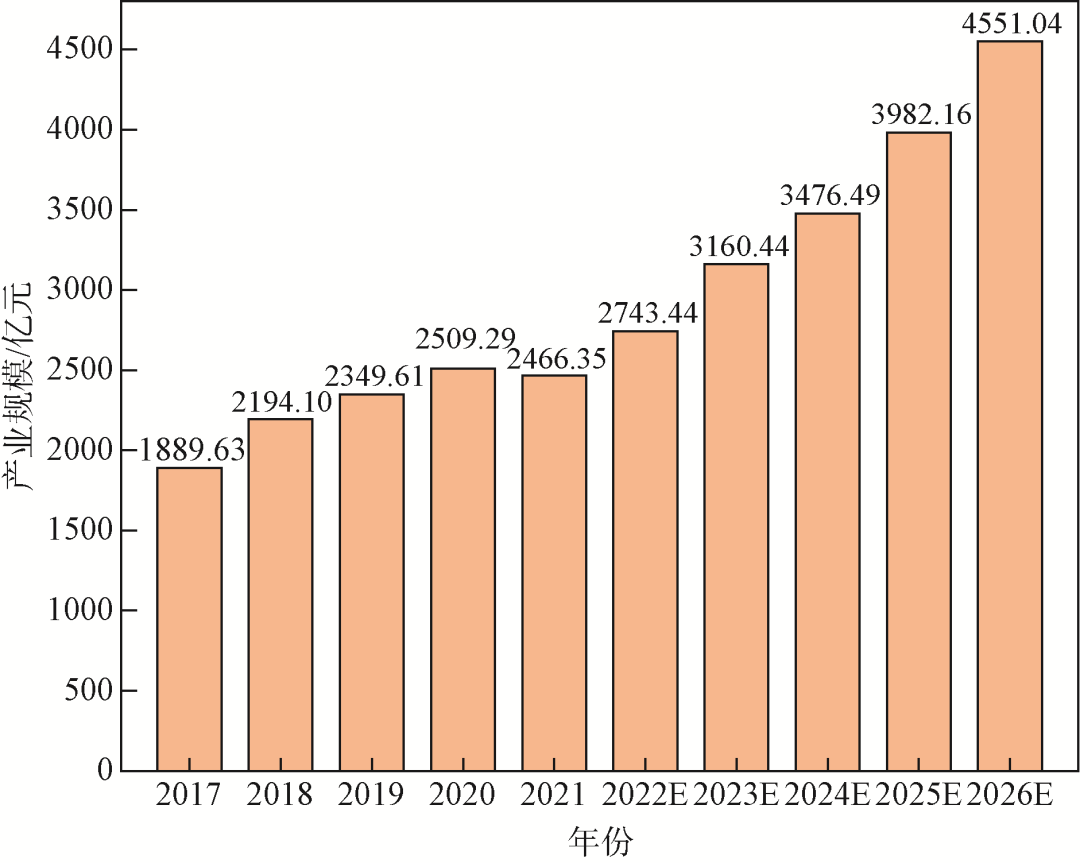

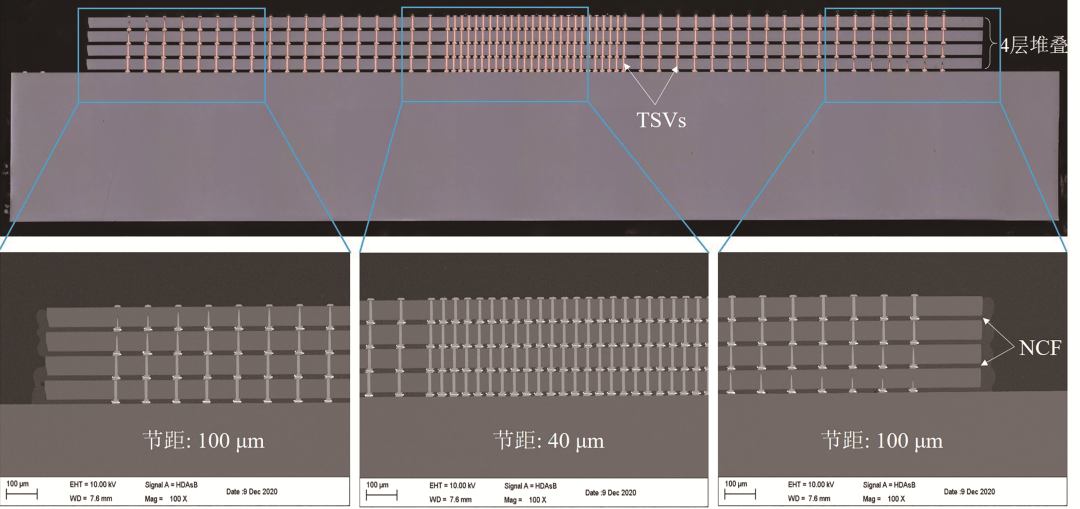

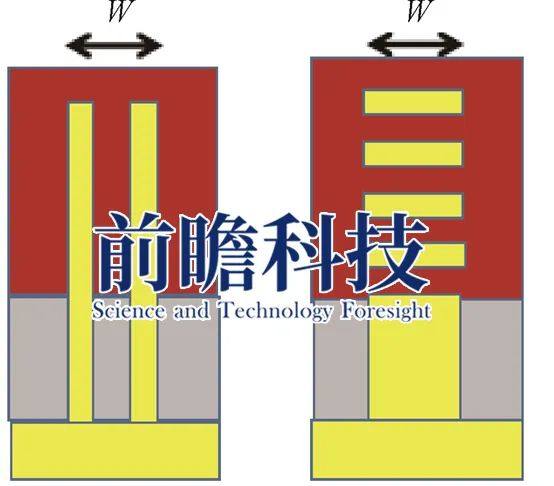

集成电路是国之重器,设计、制造和封装是集成电路产业发展的三大支柱;封装是芯片实用化的起点,是沟通芯片内部世界与外部系统的桥梁。集成电路沿着两条技术路线发展(图1),一条是持续摩尔定律,向小型化方向发展,即通过微缩互补金属氧化物半导体(Complementary Metal- Oxide-Semiconductor, CMOS)器件的晶体管栅极尺寸增加芯片晶体管数量,从而提升芯片的性能。到目前为止,工艺制程已发展至5 nm节点,主要产品为图像处理器(GPU)和中央处理器(CPU),全世界只有中国台湾积体电路制造股份有限公司(简称台积电)、美国英特尔和韩国三星等公司具备10 nm及以下节点的制造能力。另一条是超越摩尔定律,向多样化方向发展,即采用先进的封装技术将处理、模拟/射频(Radio Frequency, RF)、光电、能源、传感、生物等集成在一个系统内,进行系统级封装(System in Package, SiP),实现系统性能的提升。相比常规封装,先进封装具有小型化、轻薄化、高密度、低功耗和功能融合等优点,不仅可以提升性能、拓展功能、优化形态,相比系统级芯片(System on Chip, SoC),还可以降低成本。 图1 集成电路发展路线图 先进封装技术发展特点 封装技术的发展史是芯片性能不断提高、系统不断小型化的历史,大致分为4个阶段:第1阶段(1970年前),直插型封装,以双列直插封装(Dual In-line Package, DIP)为主;第2阶段(1970—1990年),以表面贴装技术衍生出的小外形封装(Small Outline Package, SOP)、J型引脚小外形封装(Small Outline J-leaded, SOJ)、无引脚芯片载体(Leadless Chip Carrier, LCC)、扁平方形封装(Quad Flat Package, QFP)4大封装技术和针栅阵列(Pin Grid Array, PGA)技术为主;第3阶段(1990—2000年),球栅阵列(Ball Grid Array, BGA)、芯片尺寸封装(Chip Scale Package, CSP)、倒装芯片(Flip-Chip, FC)封装等先进封装技术开始兴起;第4阶段(2000年至今),从二维封装向三维封装发展,出现了晶圆级封装(Wafer Level Package, WLP)、系统级封装、扇出型(Fan-Out, FO)封装、2.5D/3D封装、嵌入式多芯片互连桥接(Embedded Multi-die Interconnect Bridge, EMIB)等先进封装技术。 近年来,先进封装技术的内驱力已从高端智能手机领域演变为高性能计算和人工智能等领域,涉及高性能处理器、存储器、人工智能训练和推理等。 当前,除了传统委外封测代工厂(OSAT)和科研机构做封装外,晶圆代工厂(Foundry)、整合元器件制造商(IDM)、无厂半导体公司(Fabless)、原始设备制造商(OEM)都在大力发展先进封装或相关关键技术。目前台积电已成为先进封装技术创新的引领者之一,相继推出了基板上晶圆上的芯片(Chip on Wafer on Substrate, CoWoS)封装、整合扇出型(Integrated Fan-Out, InFO)封装、系统整合芯片(System on Integrated Chips, SoIC)等;英特尔推出了EMIB、Foveros和Co-EMIB等先进封装技术,力图通过2.5D、3D和埋入式3种异质集成形式实现互连带宽倍增与功耗减半的目标;三星电子推出了扇出型面板级封装(Fan-Out Panel Level Package, FOPLP)技术,在大面积的扇出型封装上进一步降低封装体的剖面高度、增强互连带宽、压缩单位面积成本,取得性价比的优势。 当前集成电路的发展受“存储墙”“面积墙”“功耗墙”和“功能墙”这“四堵墙”的制约。如图2(a)。所示,处理器的峰值算力每两年增长3.1倍,而动态存储器的带宽每两年增长1.4倍,存储器的发展速度远落后于处理器,相差1.7倍。为了突破“存储墙”,业界提出了存内计算和近存计算两种技术途径,其中存内计算的能效高、精度低;近存计算的算力高、精度高,它是一种基于先进封装的技术途径,通过超短互连技术,可实现存储器和处理器之间数据的近距离搬运。 图2 集成电路发展面临的挑战 当芯片制程相同时,通过增大芯片面积可以集成更多的晶体管数量,从而提升芯片的性能,然而,芯片尺寸受限于光刻机的光罩极限,如图2(b)所示,当前最先进的极紫外光刻机的最大光罩面积为858 mm2(26 mm×33 mm)。2020年,美国英伟达公司发布了A100 GPU芯片,采用台积电7 nm鳍式场效应晶体管(Fin Field-Effect Transistor, FinFET)工艺,通过常规手段制造了接近1个光罩面积的芯片,面积达826 mm2(~25.5 mm×32.4 mm),拥有540亿个晶体管,单精度(FP32)算力高达19.5 TFLOPS,存储带宽为2.039 TB/s。2019年,美国人工智能初创公司Cerebras System通过台积电芯片间连接技术(Cross-die Wires)推出了世界上最大的芯片,面积达到46225 mm2(215 mm×215 mm),约等于A100的56倍,存储带宽达20 PB/s,该技术虽突破了1个光罩面积,但成本极高。当前,通过先进封装技术集成多颗芯片是突破芯片“面积墙”的一种低成本主流方案。 如图2(c)所示,近年来单个GPU和CPU的热设计功耗(Thermal Design Power, TDP)逐年增大。2024年单个GPU的TDP将突破千瓦级,由多个GPU芯片和高带宽存储器(High Bandwidth Memory, HBM)阵列组成的系统,TDP可能突破万瓦级,热设计者将面临极大的挑战,为突破“功耗墙”,迫切需要采用更先进的冷却技术。 单一衬底可实现的功能有限,为突破“功能墙”,可通过多芯片异质集成技术,将传感、存储、计算、通信等不同功能的元器件集成在一起,实现电、磁、热、力等多物理场的有效融合,如图2(d)所示。 先进封装技术研究进展 以芯粒(Chiplet,又称小芯片)异质集成为核心的先进封装技术,将成为集成电路发展的关键路径和突破口。本节将介绍与芯粒相关的先进封装技术研究进展,包括芯粒异质集成技术和典型先进封装技术两部分。 2.1 芯粒异质集成技术 增大芯片尺寸可增多晶体管数量,从而可以集成更复杂的微体系结构、更多的片上存储器以及更多的内核,提高芯片性能。然而,芯片尺寸受限于光罩极限,且芯片良率随尺寸的增大而降低。如图3所示,工艺成熟后,当芯片面积从213 mm2增至777 mm2时,良率降低了33%,因此,芯片的成本随尺寸的增大而增加,芯粒异质集成技术已成为维持摩尔定律和超越光罩极限的一种有效方法。 图3 芯片良率与芯片面积的关系 采用更先进的制程也可提升芯片的性能。然而,随着工艺节点向小微缩,采用先进制程制造大芯片的成本越来越高,如图4所示。相比采用45 nm节点制造的250 mm2的芯片,采用16 nm工艺节点后,芯片每平方毫米的成本增加1倍以上,采用5 nm工艺后,成本将增加4~5倍,因此摩尔定律已从单个晶体管微缩向系统级微缩演变。芯粒是一种有效的片间互连和封装架构,即将大芯片拆分成多颗芯粒,以搭积木的形式将不同功能、不同合适工艺节点制造的芯粒封装在一起。拆解后的小芯片可形成货架产品,便于快速灵活的开发,降低开发成本与周期的同时,化整为零,极大减少了知识产权(Intellectual Property, IP)问题。同时,多种芯片的灵活集成可有效提高产品的功能性,利用常规工艺即可实现先进的集成芯片性能,从而以全新的角度解决先进制程技术局限导致的技术代际落后问题,形成芯粒异质集成的差异化竞争。 图4 芯片成本随工艺节点微缩递增 2017年8月美国国防部高级研究计划局(DARPA)的“电子复兴计划”中,正式发布了“通用异质集成和知识产权复用策略”项目(CHIPS),其目标是促成一个兼容、模块化、IP复用的芯粒生态系统,DARPA整合了军工企业、半导体企业、电子设计自动化(Electronic Design Automation, EDA)企业以及高校共同推进此项目。近年来,美国英特尔、AMD和法国原子能委员会电子与信息技术实验室(CEA-Leti)分别推出了Ponte Vecchio处理器、Zen 3 Ryzen处理器和96核处理器等芯粒产品,如图5所示。其中,Ponte Vecchio处理器集成了47个功能单元和16个散热单元,Zen 3 Ryzen处理器实现了CPU核和三级静态缓存的三维垂直堆叠,96核处理器集成了6个相同的计算芯粒。 图5 典型芯粒产品 2014年9月华为开发了首款全功能的基于台积电16 nm FinFET工艺的网络处理器,通过CoWoS封装技术集成了1个16 nm 32核ARM Cortex-A57、1颗28 nm逻辑芯片和1颗28 nm输入/输出(I/O)芯片,相比上一代产品,性能提升了3倍。 2.2 典型先进封装技术 芯粒异质集成涉及的典型先进封装技术包括硅通孔(Through Silicon Via, TSV)、超高密扇出、EMIB以及混合键合等。 2.2.1 硅通孔技术 TSV是一种垂直互连技术,它是由威廉·肖克利(William Shockley)于1958年提出的,目前应用最广泛的填铜TSV,由日本超级先锋协会首创电子技术联盟(1999—2003年)率先实现。国际半导体技术路线蓝图将TSV定义为连接硅晶圆两面并与硅衬底和其他通孔绝缘的电互连结构,其基本结构示意图如图6所示,TSV的尺寸多为10 μm×100 μm和30 μm×200 μm,开口率介于0.1%~1%。相比平面互连,TSV可减小互连长度和信号延迟,降低寄生电容和电感,实现芯片间的低功耗和高速通信,增加宽带和实现封装小型化。当前TSV主要用于硅转接板、芯片三维堆叠等方面。其中,硅转接板作为芯片和有机基板的中间层,因与硅芯片的热膨胀系数相同,在硅转接板上可集成多颗具有高密度凸点的芯片,如美国赛灵思的现场可编程门阵列(Field-Programmable Gate Array, FPGA)产品;可作为HBM和处理器的互连通道,如英伟达A100产品;可实现两颗SoC芯片的拼接,如苹果最新发布的M1 Ultra芯片。硅转接板以是否集成特定功能分为无源和有源转接板,无源转接板仅包含金属互连层,有源转接板包含可集成供电、片内网络通信等功能。芯片三维堆叠技术可通过TSV实现多芯片的短距离高速通信,HBM就是一种典型的应用。 图6 TSV基本结构示意图 1)无源转接板技术 台积电的CoWoS是一项2.5D封装技术,采用的是无源转接板,其主要工艺特点如下:①通过微凸点将多颗芯片并排键合至硅基无源转接板晶圆上,形成芯片至晶圆(Chip on Wafer, CoW)装配体;②减薄晶圆背面以露出TSV;③制备可控塌陷芯片连接(C4)凸点;④切割晶圆并将切好的晶圆倒装焊至封装基板(Substrate)上,形成最终的CoWoS封装。 图7为台积电CoWoS封装技术路线。自2012年起,该技术已发展5代,通过掩膜版拼接技术,无源转接板尺寸从接近1个光罩面积增至3个光罩面积(2500 mm2)。前两代为同质芯片集成,主要集成硅基逻辑芯片,从第3代起演变为异质芯片集成,主要集成逻辑SoC芯片和HBM阵列。为提高芯片的电源完整性,其开始在无源转接板内集成深沟槽电容。 图7 台积电CoWoS封装技术路线 2011年,赛灵思推出了当时世界上最大的FPGA产品。为了解决大芯片良率低的问题,该公司采用台积电的第1代CoWoS封装技术(图8),将4颗28 nm FPGA小芯片组装在1个100 μm厚采用65 nm工艺制造的无源转接板上,每颗芯粒的尺寸为7 mm×12 mm,硅转接板尺寸为25 mm×31 mm,接近1个光罩面积,基板为10层FCBGA基板,尺寸为42.5 mm×42.5 mm。 图8 赛灵思FPGA CoWoS封装 2020年,英伟达采用台积电第4代CoWoS技术封装了其A100 GPU系列产品(图9(a)),将1颗英伟达A100 GPU芯片和6个三星电子的HBM2集成在一个1700 mm2的无源转接板上,每个HBM2集成1颗逻辑芯片和8个动态随机存取存储器(DRAM),基板为12层倒装芯片球栅格阵列(Flip-Chip Ball Grid Array, FCBGA)基板(图9(b)),尺寸为55 mm×55 mm。 图9 英伟达A100 GPU CoWoS封装 2)有源转接板技术 有源转接板是无源转接板的技术延伸,在无源转接板内部集成一些功能单元。法国CEA-Leti开发了一款基于65 nm CMOS工艺的有源转接板,面积约200 mm2,拥有1500万个晶体管,7层金属,集成了可近距离直接给芯片供电的开关式电容电压调节器(Switching Capacitor Voltage Regulator, SCVR)、片间通信的分布式片上网络、片外通信的系统I/O以及可测性设计(Design For Test, DFT)等功能。采用20 μm间距的微凸点,将6个基于28 nm全耗尽型绝缘体上硅(Fully Depleted Silicon-On-Insulator, FDSOI)工艺的计算芯粒和一个基于65 nm CMOS工艺的有源转接板面对面热压键合在一起,每颗芯粒的面积为22.4 mm2,拥有3.95亿个晶体管,16核,集成后总共有96核,实现了220 GOPS的系统算力,电压转换效率为82%,芯片间互连带宽密度为3 Tb/(s·mm-2),能效为0.59 pJ/b(图10)。英特尔开发了一款基于22 nm工艺的有源转接板,包含11层金属和TSV,TSV与顶部金属层相邻,面积为90.85 mm2,集成了供电、PCIe Gen3、USB Type C等功能。通过Foveros技术将基于10 nm FinFET先进工艺的计算芯片和22 nm成熟工艺的有源转接板面对面连接在一起,如图11所示。其中,计算芯片有13层金属,面积为82.5 mm2,融合了混合CPU架构、图像等功能。 图10 CEA-Leti 96核处理器集成技术 图11 英特尔Foveros技术 3)HBM技术 如前所述,存储器的“存储墙”限制了计算芯片性能的发挥,第5版图形用双倍数据传输率存储器(GDDR5)的带宽极限为32 GB/s,由逻辑芯片和多层DRAM堆叠而成的HBM技术突破了带宽瓶颈,HBM1和HBM2的带宽分别为128 GB/s和256 GB/s,未来HBM3可突破1.075 TB/s。当片外存储从并排布局图形用双倍数据传输率(Graphics Double Data Rate, GDDR)存储器转为三维堆叠HBM,容量为1 GB时,HBM模组占用面积减少94%,如图12(a)和图12(b)所示。第1代HBM的架构如图13(a)所示,由逻辑芯片和4层DRAM堆叠在一起,每个HBM有8个通道,每个通道有128个I/O,因此每个HBM有1024个I/O,即1024个TSV,位于HBM的中间区域。存储器和处理器通过无源转接板上的再布线层(Re-Distributed Layer, RDL)将HBM逻辑芯片的端口物理层(Port Physical Layer, PHY)与处理器的PHY连接在一起,如图13(b)所示。 图12 片外存储从并排布局转为三维堆叠 图13 HBM架构和封装集成示意图 2.2.2 超高密度扇出技术 2020年,台积电发布了一种超高密度扇出封装技术,即集成扇出型晶圆上系统(InFO_SoW),如图14所示,通过超高密度扇出封装技术将多颗好的晶粒(Known Good Die, KGD)、供电、散热模块和连接器紧凑地集成在晶圆上,包含6层RDL,前3层线宽/线距为5/5 μm,用于细线路芯片间互连;后3层线宽/线距为15/20 μm,用于供电和连接器互连。相比印制电路板(Printed Circuit Board, PCB)级多芯片模块,InFO_SoW具有高带宽、低延迟和低功耗的特点。 图14 台积电InFO_SoW技术 2021年8月19日,特斯拉人工智能(Artificial Intelligence, AI)日推出了其自研的面向AI专用领域的Dojo D1芯片,如图15(a)所示。D1芯片采用台积电7 nm工艺,面积为645 mm2,晶体管数量达500亿个,1 mm2面积上的晶体管数量已超过英伟达A100芯片,包含354个训练节点,BF16/CFP8的峰值算力高达362 TFLOPS,TDP为400 W。通过台积电InFO_SoW封装技术将25颗D1芯片集成在一起,再将供电、散热、连接器等模块集成进来,形成1个Dojo训练Tile,BF16/CFP8算力高达9.1 PFLOPS,如图15(b)所示。将120个Dojo训练Tile组装成了ExaPOD超级计算机,ExaPOD含有3000颗D1芯片,106.2万个训练节点,BF16/CFP8算力可以达到1.1 EFLOPS。表1对比了英伟达A100芯片与特斯拉Dojo训练Tile的主要性能指标。从表1中可以看出,晶圆级片上大规模集成可大幅提升系统算力和带宽,是提升系统能力的一种重要途径。 图15 特斯拉Dojo D1芯片晶圆级片上大规模集成 表1 英伟达A100芯片与特斯拉Dojo训练Tile主要性能指标对比 2.2.3 EMIB技术 EMIB技术最早由英特尔的Mahajan和Sane于2008年提出,后又经Braunisch和Starkston等改进,近年来已发展成为英特尔最具代表性的先进封装技术之一,已用于其多款FPGA产品,如Agilex FPGA和Direct RF FPGA。它是在有机基板中埋入若干超薄的(厚度一般小于100 μm)、高密度的硅桥,实现两两芯片间的互连,如图16所示。目前英特尔可量产的硅桥尺寸为2 mm×2 mm~12 mm×12 mm,包含4层RDL和1层焊盘,线宽/线距为1 μm/1 μm。EMIB可提供芯片间局部高密度互连,可灵活地放置在基板任意需要互连的地方,不限制芯片的集成数量与位置,不影响基板上其他线路的布局布线。 图16 英特尔EMIB互连技术 2.2.4 混合键合技术 图17为键合技术的演进,其中混合键合是通过铜—铜金属键合和二氧化硅—二氧化硅介质层键合实现无凸点永久键合的芯片三维堆叠高密度互连技术,可实现极小间距的芯片焊盘互连,每平方毫米可互连的芯片焊盘数为104~106个,可以提供更高的互连密度、更小更简单的电路、更大的带宽、更小的电容和更低的功耗。与传统C4焊点和微凸点连接技术相比,混合键合技术的主要优点有:①实现芯片之间无凸点互连,微凸点的取消将进一步降低芯片之间通道的寄生电感和信号延时;②实现芯片之间超细间距的互连,比微凸点提高10倍以上,超细间距的互连将增加布线有效使用面积,大幅增加通道数量,实现数据处理串并转换,简化I/O端口电路,增大带宽;③实现超薄芯片制备,通过芯片减薄可使芯片厚度和重量大幅降低,并且可进一步提升系统中芯片的互连带宽;④实现键合可靠性的提高,铜—铜触点间以分子尺度融合,取消了焊料连接,二氧化硅—二氧化硅以分子共价键键合取消了底填材料,极大提高了界面键合强度,增强了芯片的环境适应性。 图17 键合技术的演进 美国AMD通过混合键合技术将两个64 MB三级静态缓存芯片和1个含TSV的8核CPU垂直键合在一起,实现了3D芯粒,如图18所示,其混合键合的间距为9 μm,互连密度约12345个/mm2,相比间距为36 μm的微凸点,互连密度提升大于15倍,互连能效提升大于3倍。 图18 AMD 3D芯粒技术 2022年3月,英国AI芯片公司Graphcore发布了一款智能处理单元(Intelligent Processing Unit, IPU)产品Bow,其结构示意图如图19所示,采用台积电SoIC-WoW(Wafer on Wafer,晶圆对晶圆)混合键合技术,将7 nm的处理器晶圆和供电晶圆堆叠在一起。其中,供电晶圆上含有深沟槽电容,用来存储电荷,背面TSV允许互连至晶圆内层;较上一代相同7 nm制程,采用3D WoW封装技术后,性能提升40%,功耗降低16%。 图19 台积电SoIC-WoW混合键合技术 中国大陆先进封装技术发展现状 和存在的问题 中国大陆封装测试(简称封测)企业主要集中于长江三角洲地区,根据中国半导体行业协会统计,2020年中国大陆封测产品销售额达到2509.29亿元,江苏、上海、浙江3个省份2020年封测产品销售额合计达到1838.3亿元,占2020年中国大陆封测产品销售额的73.3%。2021年中国大陆封测产品销售额降至2466.35亿元,同比下降1.7%,2022年将再次增长,预计增至2743.44亿元,同比增长11.2%,预计2026年中国大陆集成电路封测市场规模将达4551.04亿元,如图20所示。包括BGA、CSP、WLP、FO、SiP和2.5D/3D等在内的先进封装业务占比也逐年上升,2021年中国大陆规模以上的集成电路封测企业先进封装产品销售额占整个封装产业的35%左右,在保持增长势头的同时,与国际大厂仍有不小的差距。 图20 2017—2026年中国大陆封测市场规模及预测 目前中国大陆产业领头羊多注重基于解决集成电路工艺瓶颈的产业化,对于核心高端产品技术以及面向多功能与集成度的前瞻性技术缺乏相关技术布局。以长电科技、通富微电、华天科技、华进半导体为代表的封装企业,在WLP、SiP及三维堆叠等方向实现部分产品量产与应用。开展先进封装主要的研究机构,如中国科学院微电子研究所、中国科学院上海微系统与信息技术研究所、清华大学、北京大学、武汉大学、华中科技大学、北京理工大学、桂林电子科技大学、中国电子科技集团有限公司、中国航天科技集团有限公司等单位已形成了较强的研发力量,在晶圆级/板级扇出型封装、异质芯片2.5D集成、Si基芯片3D叠层封装等技术方面,经过长期的实践摸索,形成的技术积累缩短了与国外先进封装技术的差距。图21为中国科学院微电子研究所联合华进半导体开发的三维堆叠芯片封装。 图21 中国科学院微电子研究所联合华进半导体开发的三维堆叠芯片封装 与世界先进水平相比,中国大陆先进封装技术存在以下问题。 (1)目前中国大陆封装领域总体仍以传统的中低端封装为主,从先进封装营收占总营收的比例和高密度集成等先进封装技术发展方面,仅FC技术相对成熟,而以TSV为代表的2.5D/3D封装和以扇出型封装为代表的高密度扇出型技术,与国外公司的技术差距明显,在先进封装全球产业链中仍未占据重要位置,中国大陆总体先进封装技术水平与国际领先水平还有一定的差距。未来对高端先进封装技术的需求将越来越多,因此实现高端先进封装技术突破越来越重要。 (2)先进封装关键装备及材料尚未实现自主可控。支撑中国大陆封装产业链发展的整体基础技术水平不高,先进封测技术所需的关键封装、测试设备和材料主要依赖进口,难以满足市场需求。 (3)先进封装设计主要依赖境外商用EDA工具,中国大陆封装级EDA还处于起步阶段,与境外主流EDA厂商差距比较明显,市场占有率较低,用户反馈和迭代次数少,导致中国大陆EDA工具发展缓慢。 中国大陆先进封装技术发展建议 针对中国大陆先进封装领域的薄弱环节,重点攻关核心封装工艺、关键封装装备及材料痛点,加快布局EDA工具,推进中国大陆集成电路封装领域自主可控高质量发展。 (1)先进封装工艺。基于明确的产业应用需求,开发合适的封装工艺,并重点攻关核心封装工艺,对于需在前道平台上加工的部分工艺,需明确前道和后道工艺分工,进行前、后道协同设计和迭代优化。 (2)核心封装材料。首先形成良好的材料—封装—应用产业链,基于产业应用需求,对标国外进口材料,材料厂商开发相应的封装材料,并测试评估和比较材料性能。然后,在国内先进封装平台上进行多轮迭代使用,最终实现进口材料国产化替代。 (3)关键封装装备。随着应用需求的不断递进,先进封装技术不断升级,封装厂商需向装备厂商提出明确的需求,并与设备厂商协同开发关键封装装备。然后,在国内先进封装平台上,加快国产装备的试用和迭代。 (4)EDA工具。发展国产EDA工具是一个漫长的过程,需要用户不断反馈和软件迭代。发展国产EDA工具不仅仅局限于EDA算法和点工具研究,还需做好规划,具有集成能力,最终形成自主可控的EDA平台。 (5)产业链。预防美国针对中国大陆集成电路高端技术的进一步出口管制,加快发展中国大陆集成电路封装领域创新联合体,强化建设先进封装联合攻关公共平台,完善国内芯粒异质集成产业链。 结束语 近年来,以高性能计算、人工智能和5G通信为代表的需求牵引,加速了集成电路的发展,以尺寸微缩为主线的摩尔定律发展放缓,22 nm工艺节点以下芯片的设计和制造成本呈指数级增加,芯片尺寸受限于光刻机的最大曝光面积,单一衬底上可集成的功能有限,SoC单片向芯粒异质集成“改道”是集成电路发展的重要趋势。依据功能划分,将原先的大尺寸SoC芯片拆成芯粒,主要功能采用先进制程,次要功能采用成熟制程,再通过先进封装技术,实现成本较低、性能接近的集成电路产品,其中先进封装技术不再局限于后道工艺,一些关键工艺需在前道平台上进行,因此需进行前后道协同设计开发。中国需快速布局芯粒领域的技术研发,通过路径创新,降低中国大陆集成电路发展同集成电路既有全球体系直接对冲的风险,实现灵活、高效、系统级的新型集成电路发展模式,推动集成电路的创新发展与自主可控。 END 往期推荐

● 综述与述评 |刘伟平:EDA产业与IP核产业发展现状及发展趋势

● 综述与述评 | 倪光南院士:聚焦开源RISC-V发展中国芯片产业

关于本刊 《前瞻科技》是由中国科学技术协会主管,科技导报社主办、出版的科技智库型自然科学综合类学术期刊,于2022年创刊。 办刊宗旨:围绕国家重大战略任务、科技前沿重要领域和关键核心技术,刊载相关研究成果的综述和述评,促进学术交流,推动科技进步,服务我国经济社会高质量发展。 常设栏目有“前瞻”“综述与述评”“聚焦”“论坛”“文化”“书评”等,其中“前瞻”“综述与述评”为固定栏目,其他为非固定栏目。 期刊官网:www.qianzhankeji.cn

长按识别二维码关注我们

点击“阅读原文”直达期刊官网,查看全文精彩内容

(来源:Graphcore公司)

(来源:中国半导体行业协会)

● 综述与述评 | 卜伟海:后摩尔时代集成电路产业技术的发展趋势

● 综述与述评 | 张卫:先进CMOS制造工艺的技术演进及自主发展思考

原文始发于微信公众号(半导体设备与材料):综述与述评 | 曹立强,侯峰泽:先进封装技术的发展与机遇