作者简介

作者:Friedrichs Peter, Vice President SiC,

Infineon Technologies AG

翻译:赵佳

“ 除了性能之外,可靠性和坚固性是SiC MOSFET讨论最多的话题。我们将坚固性定义为器件承受特定的特殊压力事件的能力,例如,短路能力或脉冲电流处理能力。可靠性指器件在目标寿命内额定工作条件下的稳定性。与可靠性相关的现象包括某些电气参数的漂移或毁坏性的故障。对于硬故障,通常以FIT率的形式进行量化。FIT率说明了某一类型的设备在一定时期内预期有多少次故障。目前,宇宙射线效应主要制约着大功率硅器件的FIT率。

就SiC而言,还需要考虑由于栅氧化层电场应力造成的栅极氧化层可靠性问题。如下图所示,SiC的总FIT率是宇宙射线FIT率和氧化物FIT率之和。对于宇宙射线失效率,可以通过实验的方式得到某种技术的FIT率,根据这些结果并结合应用的目标,就可以实现一个符合目标FIT率的产品设计。优化漂移区的电场设计通常可以实现低的FIT率。对于氧化物的FIT率,则需要应用一个筛选过程来降低FIT率,因为与硅相比,SiC的缺陷密度仍然相当高。然而,即使在我们的硅功率器件中,栅极氧化物的筛选仍然是作为一种质量保证措施而采用的.

SiC MOS器件的栅极氧化物可靠性的挑战是,在某些工业应用给定的工作条件下,保证最大故障率低于1 FIT,这与今天的IGBT故障率相当。

由于碳化硅和硅材料上生长的二氧化硅(SiO2)的质量和特性几乎是相同的,因此理论上相同面积和氧化层厚度的Si MOSFET和SiC MOSFET可以在相同的时间内承受大致相同的氧化层电场应力(相同的本征寿命)。但是,这只有在器件不包含与缺陷有关的杂质,即非本征缺陷时才有效。与Si MOSFET相比,现阶段SiC MOSFET栅极氧化物中的非本征缺陷密度要高得多。 电筛选降低了可靠性风险

与没有缺陷的器件相比,有非本征缺陷的器件更早出现故障。无缺陷的器件虽然也会疲劳失效,但寿命很长。通常情况下,足够厚的无缺陷氧化层的本征失效时间比正常应用下的使用时间要长几个数量级。因此,在典型的芯片寿命内,氧化物的FIT率完全由非本征缺陷决定。

保证碳化硅MOSFET的栅极氧化层具有足够的可靠性的挑战是——如何将受非本征缺陷影响的器件数量,从最初工序结束时的高比例(如1%),减少到产品发运给客户时可接受的低比例(如10ppm)。实现这一目标的一个公认的方法是使用电筛选。

在电筛选过程中,每个器件都处于栅控应力模式。应力模式的选择方式是,具有严重缺陷的器件将失效,而没有这些缺陷的器件,或只有非关键性缺陷的器件可以通过测试。未通过筛选的器件将从产线移除。通过这种方式,我们将潜在的可靠性风险转换为产量损失。

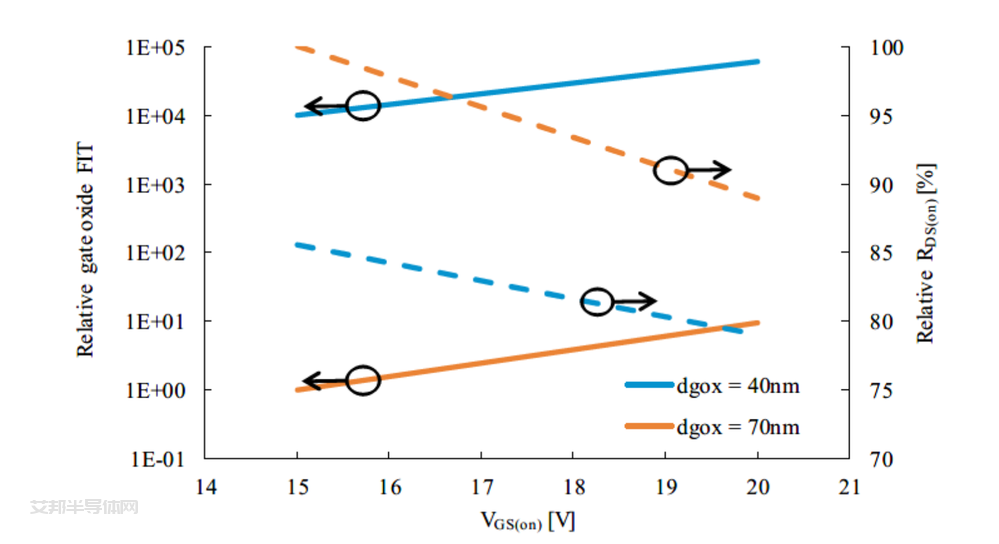

为了使器件能够承受一定的栅极应力,栅极氧化层需要有一个特定的最小厚度。如果栅极氧化层的厚度太低,器件在筛选过程中会因为疲劳而出现本征失效,或者在筛选后出现阈值电压和沟道迁移率下降的情况。另一方面,更厚的栅极氧化层会增加阈值电压,并在给定的VGS(on)条件下降低沟道电导率。下图说明了栅极氧化物FIT率和器件性能之间的权衡,这在中也有讨论。

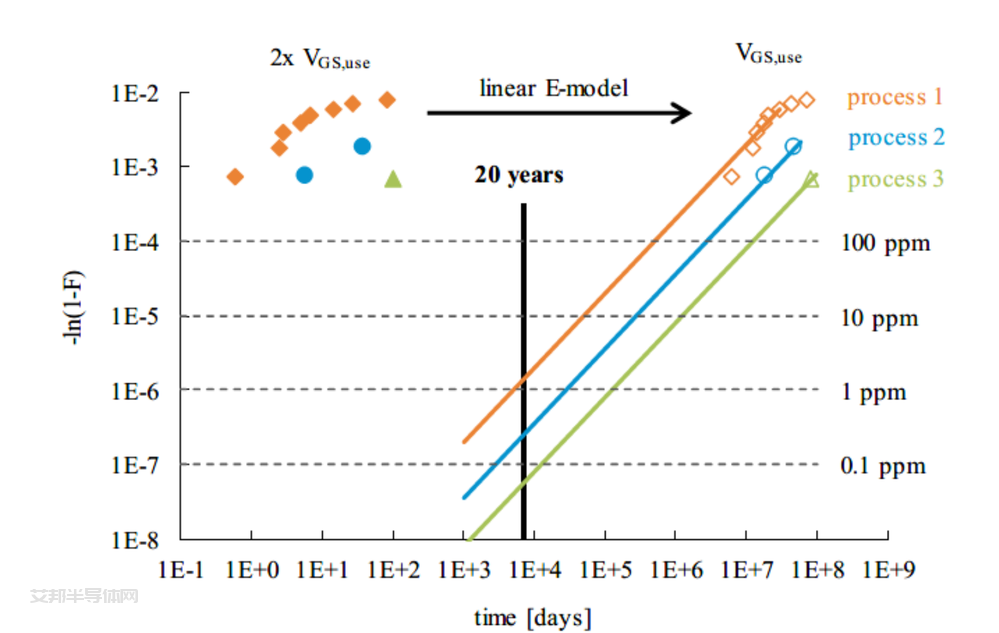

我们已经投入了大量的时间和样品,得到了SiC MOSFET的栅氧化可靠性的大量数据。举例来说,我们对通过电筛选的SiC MOSFET分成三组,每组施加不同的正负栅极应力偏置,在150℃下测试了的通态可靠性100天。每组样品有1000个器件。下图显示了不同栅极氧化工艺条件下的结果,最终量产的工艺可靠性方面有明显改进。

使用初始的工艺条件,在两倍于建议的30V栅极偏压下,1000个器件中只有不到10个失效。改进的实施工艺将这一数字减少到30V时仅有一个故障,25V和-15V时的故障为零。惟一的一个失效是非固有失效,然而,这并不关键,因为在额定的栅极偏压使用条件下,失效发生的时间点会远远超过规定的产品寿命。

当然,除了评估通态氧化物的可靠性外,评估断态氧化物的应力也很重要,因为SiC功率器件中的电场条件比硅功率MOS元件更接近SiO2的极限。

屏蔽是导通电阻和可靠性之间的权衡

关键的策略是通过对深p阱的适当设计来有效地屏蔽敏感的氧化物区域。屏蔽的效率是导通电阻和可靠性之间的权衡。在沟槽MOSFET中,深p阱在MOSFET的沟道区下面形成类似JFET的结构,可以有效地促进屏蔽。这种JFET(结型场效应晶体管)为导通电阻增加了一个额外的分量,主要取决于掩埋的p区之间的距离和掺杂。这种屏蔽结构的设计特点对于避免关断状态下的栅极氧化层退化或栅极氧化层击穿至关重要。

为了验证CoolSiC™ MOSFET的断态可靠性,我们在150°C、VGS=-5V和VDS=1000V的条件下对超过5000个1200V的SiC MOSFET进行了100天的应力测试。这些条件对应于工业应用已经够严酷了。受器件的击穿电压的限制,VDS不能再继续增加。

在更高的漏极电压下进行测试会使结果失真,因为其他故障机制,如宇宙射线引起的故障可能出现。结果是,在这次断态可靠性测试中,没有一个被测试的器件发生故障。由于650V器件遵循与1200V器件相同的设计标准,因此预计会有相同的可靠性。

原文始发于微信公众号(英飞凌工业半导体):SiC MOSFET FIT率和栅极氧化物可靠性的关系