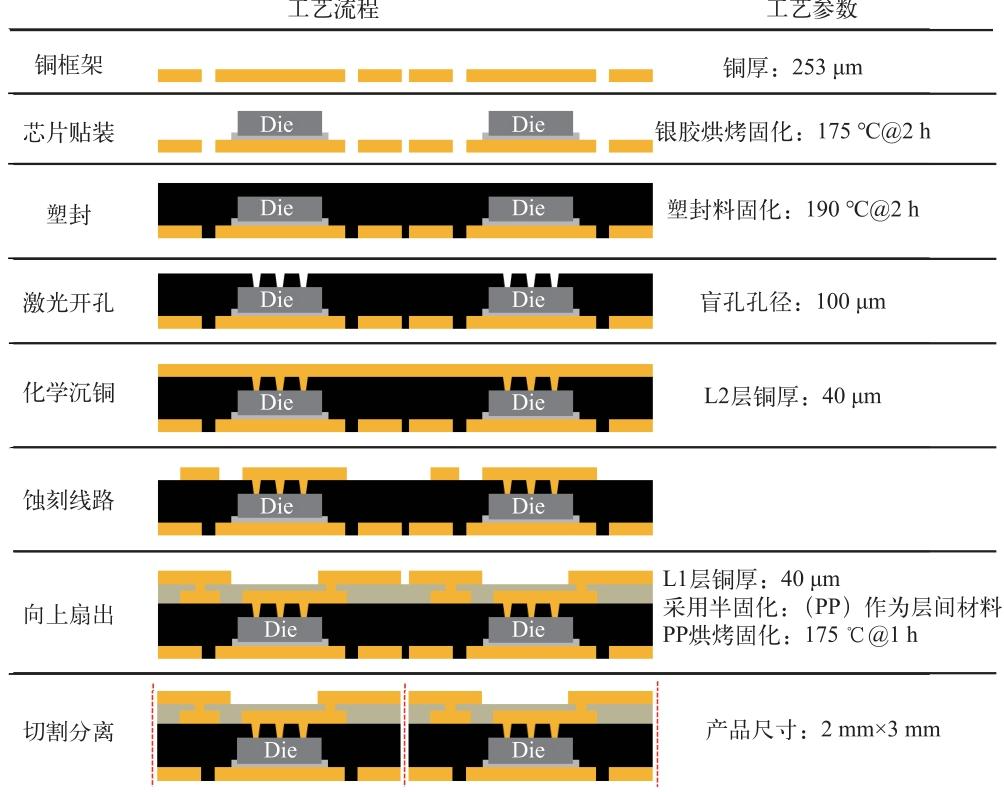

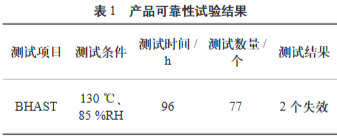

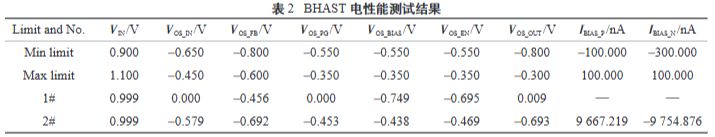

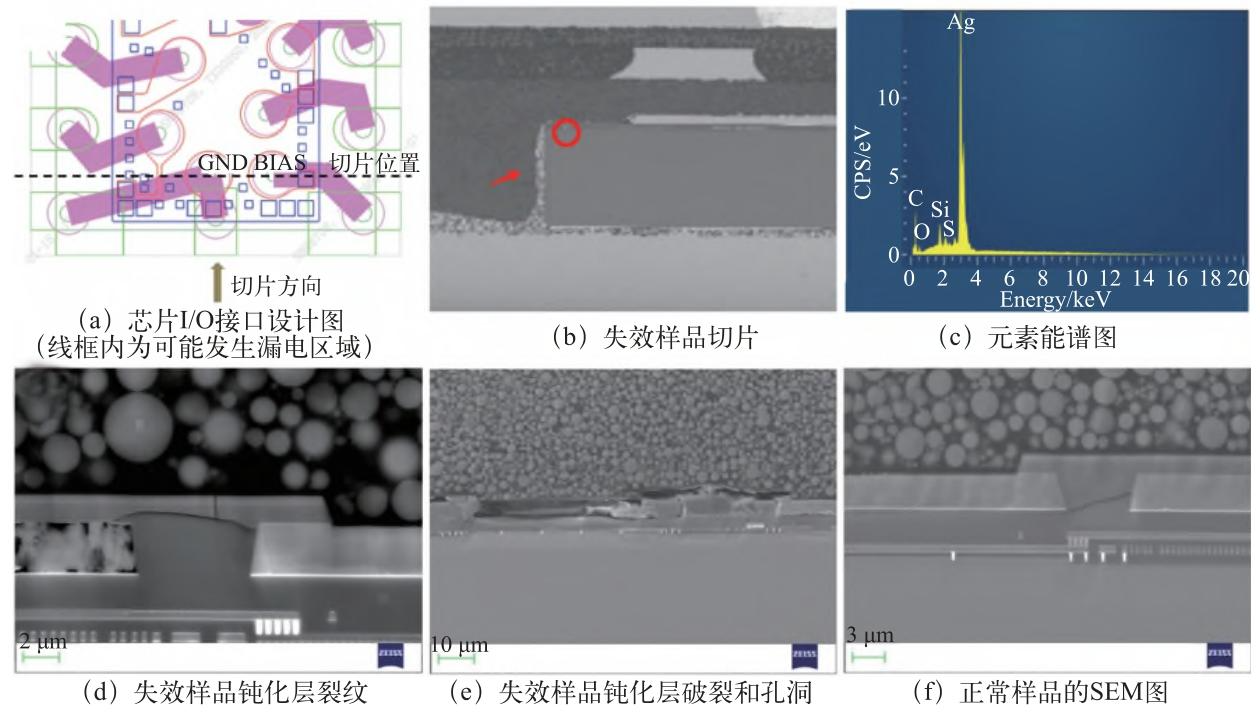

随着封装工艺的进步,扇出型板级封装(FOPLP)工艺因其具有高集成度、低成本、更好的性能和更广泛的应用领域等优势而备受关注。针对基于FOPLP工艺封装的多I/O芯片产品可靠性开展了系统研究。探索和分析了产品在偏压高加速温湿度应力测试(BHAST)中的漏电问题,根据失效分析结果,将重点聚焦于爬胶高度和产品应力。同时,通过试验设计(DOE)验证了改善产品的银胶量和固定加工参数。针对多I/O芯片应力问题,采用仿真模拟优化应力分布,产品成功通过 BHAST可靠性测试,满足130℃、85% RH条件下连续工作 264h的BHAST可靠性要求,对提升多I/O类产品整体性能和市场竞争力具有重要意义。

0 引言

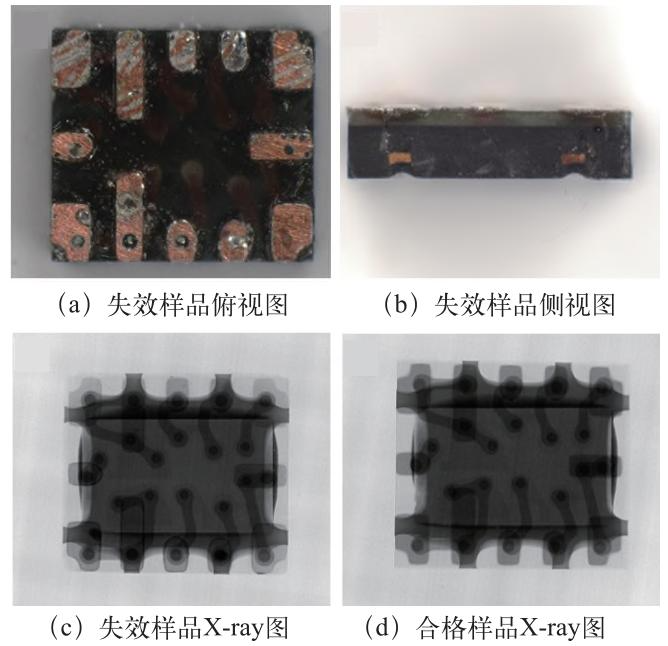

图2 测试样品外观及X-ray图

2 可靠性优化

2.1 爬胶高度改善

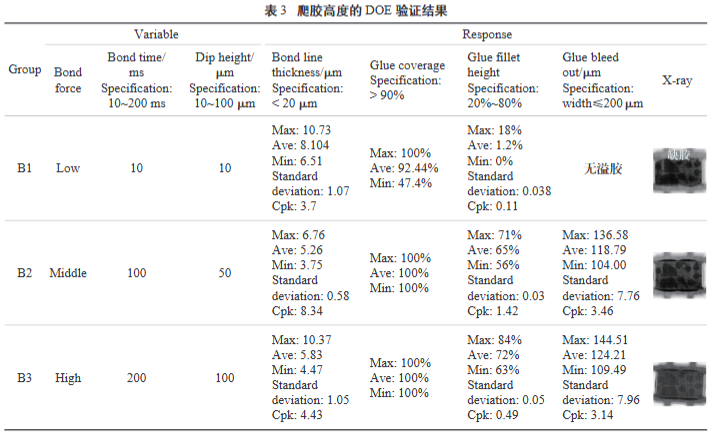

根据失效分析结果,首先需要控制产品贴片过程中的点胶量,以降低爬胶高度。针对爬胶高度进行系列DOE验证,通过固定设备参数来控制银胶的爬胶高度。主要研究了点胶力度、时间和高度3个因素,评估了芯片背面银胶厚度、覆盖率、爬胶高度和溢胶范围,结果如表3所示。

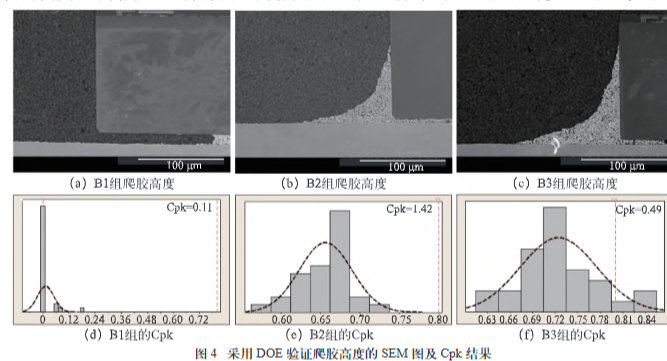

当点胶力度为低、时间为10ms、高度为10μm 时(B1 组),芯片爬胶情况如图4(a)所示,爬胶高度太低且背面存在银胶孔洞,不符合要求。当点胶力度为高、时间为200ms、高度为100μm 时(B3组),芯片爬胶情况如图4(c)所示,爬胶高度偏高。因此,选择点胶力度为中、时间为100ms、高度为50μm 的参数(B2)组,该条件下爬胶高度如图4(b)所示,爬胶高度得到了明显的控制。计算各条件下工序的制程能力指数(Cpk),结果分别如图4(d)(e)(f)所示,B1组的银胶量较少,大量样品没有形成爬胶,因此其Cpk较小,不具备参考价值。通过计算得到B2、B3组的Cpk分别为 1.42和0.49,进一步证明了B2组装片工序能够满足产品加工需求。通过DOE固定了加工参数,成功控制了加工过程中的产品银胶量,避免了银迁移现象的发生。

图4 采用DOE验证爬胶高度的SEM图及Cpk结果

2.2 应力分布优化

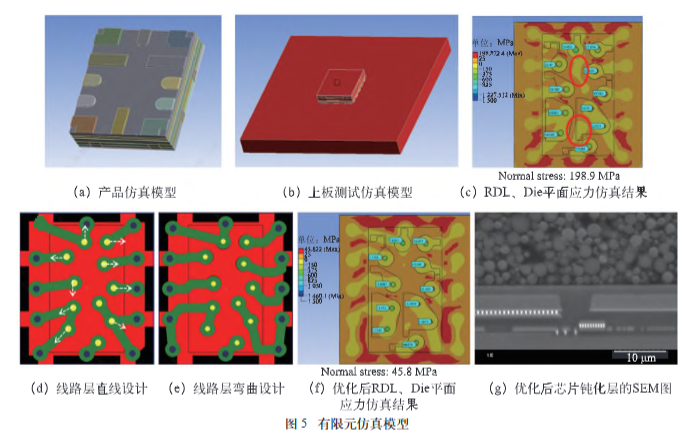

应力是物理学中的一个重要概念,指的是物体在受到外力、湿度变化、温度场变化等因素的影响而发生变形时,在物体内各部分之间产生的相互作用的内力。这种内力存在的目的是为了抵抗外因作用,并试图使物体从变形后的状态恢复到变形前的状态。为了在生产加工前评估优化策略的可行性,课题组开展了有限元应力仿真,该方法将连续体转化为由有限数量单元组成的离散模型,利用位移函数对离散模型进行数值求解。该方法灵活性强,适用范围广,因此被广泛应用于焊接热传导、焊接热弹塑性应力、焊接变形预测和焊接结构的断裂分析等领域。本次有限元仿真采用导入几何模型的方式建模。分别构建了芯片、银胶、塑封层、线路层和载板的模型,将独立模型组合成装配体,即为产品实体结构模型,产品仿真模型如图5(a)所示。为了模拟产品焊接在基板上进行可靠性测试的实际焊接条件,设置相应的边界条件,模拟将产品焊接在基板上,应力仿真模型如图5(b)所示。模拟产品在锡膏固化条件下的温度变化过程,设置温度变化条件为25~220℃,探究产品在温度变化条件下的应力情况。

针对BHAST失效分析中的产品钝化层裂纹问题,初步仿真了产品的应力分布及应力大小,RDL、Die平面应力仿真如图5(c)所示,产品RDL 盲孔到芯片面具有较大的法向应力,其数值为198.9MPa。产品盲孔集中区域(红圈部分)应力分布较大,并且此区域与产品BHAST失效分析所确定的区域相吻合。通常由于多I/O芯片表面钻孔数量较多且孔的集中程度高应力分布不均是其封装过程中的常见问题之一。

根据热应力仿真结果对产品结构进行了优化,以改善产品的应力分布,具体措施包括:1)加厚线路层与焊盘层间的半固化片,有效阻隔了应力传递;2)将线路布局由直线型优化为弯曲型,设计如图5(d)(e)所示,大幅减少了内部应力沿线路的传导;3)对芯片应力集中区域的盲孔进行外扩处理,进一步降低了整体应力分布。优化后RDL,Die平面应力仿真结果如图5(f)所示,RDL盲孔到芯片面的法向应力为 45.8MPa,相比原版本的法向应力有了显著的改善。并且芯片中心盲孔集中区域的应力分布也得到了优化,充分证明优化方案具备减弱产品应力的能力。

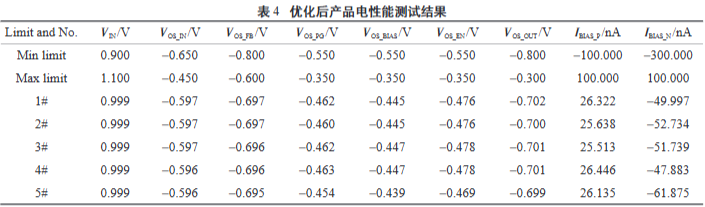

在随后的可靠性试验中,优化后产品顺利通过所有的测试项目,满足BHAST 264h(130°C,85%RH)的可靠性要求,并且在该条件下保持528h 后电性能依然符合要求,其性能指标远超既定标准,电性能测试结果如表4所示。

化后芯片钝化层的SEM图,在芯片钝化层上未发现裂纹等现象。这一优化方案的实施,不仅彻底解决了多I/O芯片产品的应力问题,并为应力改善积累了改善方案与加工检验方法。这一系列成果充分证明了采用FOPLP技术的多I/O产品器件在性能指标及长期可靠性方面的显著优势。

3 结论

本文以采用FOPLP技术的多I/O芯片产品为研究对象,详细介绍了其封装结构及加工流程,同时针对封装产品进行了可靠性测试和失效分析,通过优化贴片过程中的银胶高度控制,避免了银迁移现象发生。基于可靠性研究及应力仿真,证明了加厚产品线路层与焊盘层间的半固化片、采用线路弯曲设计和优化盲孔位置均有利于优化多I/O芯片封装的应力分布,有效解决了产品应力问题。优化后的产品成功通过了BHAST可靠性项目,为多I/O芯片的FOPLP可靠性提供了生产经验和技术参考。

来源:《电子与封装》2025年2月刊封面文章

艾邦建有半导体先进封装之FOPLP交流群,可以加强产业链的合作,促成各企业的需求对接,同时您也可以与行业精英共同探讨前沿动态,共享资源,交流经验,欢迎您的加入。

第四届功率半导体产业论坛

6月13日 苏州

|

时间 |

议题 |

演讲单位 |

|

08:45-09:00 |

开场致辞 |

艾邦创始人江耀贵 |

|

09:00-09:30 |

IGBT在工业驱动器的应用技术与探讨 |

汇川技术IPU 部门经理 李高显 |

|

09:30-10:00 |

功率半导体IGBT器件在新能源车上的应用 |

陆芯电子市场技术总监曾祥幼 |

|

10:00-10:30 |

茶歇 |

|

|

10:30-11:00 |

半导体功率模块真空灌胶方案的探讨 |

苏州韩迅总经理朱洲山 |

|

11:00-11:30 |

轻蜓AI+3D技术助力功率半导体视觉检测 |

轻蜓光电SEMI业务&市场负责人 殷习全 |

|

11:30-12:00 |

第三代半导体高性能高可靠性塑封料的开发与应用 |

衡所华威电子研发工程师刘建 |

|

12:00-13:30 |

午餐 |

|

|

13:30-14:00 |

碳化硅车载功率模块用MOSFET及其可靠性研究 |

瞻芯电子副总经理曹峻 |

|

14:00-14:30 |

纳米金属烧结技术国产化助力功率模块降本 |

清连科技董事长贾强 |

|

14:30-15:00 |

车规功率器件可靠性认证分析与SIC适用性探讨 |

SGS AEC-Q认证授权签字人 Niko Ren |

|

15:00-15:30 |

高性能功率模块铜互连的技术演进与工艺实践 |

哈尔滨理工大学教授刘洋 |

|

15:30-16:00 |

茶歇 |

|

|

16:00-16:30 |

电动汽车电机控制器的设计与制造技术 |

伟创力工程经理张润平 |

|

16:30-17:00 |

车规级SiC芯片及模块的创新进展及未来挑战 |

中电科五十五所国扬电子副总经理 刘奥 |

|

17:00-17:30 |

动力域控制器关键技术探讨 |

重庆青山工业前瞻技术研究院电气副总工程师徐志鹏 |

|

17:30-18:00 |

碳化硅芯片在车规应用中的挑战和前瞻 |

芯粤能半导体业务发展总监胡学清 |

|

18:00-20:00 |

晚宴 |

|

Nico肖 136 8495 3640(同微信)

邮箱:ab012@aibang.com

方式二:长按二维码扫码在线登记报名

https://www.aibang360.com/m/100230?ref=172672

第五届陶瓷基板及封装产业论坛

6月12日 苏州

|

时间 |

议题 |

演讲嘉宾 |

|

08:45-09:00 |

开场词 |

艾邦智造创始人江耀贵 |

|

09:00-09:30 |

金属化陶瓷基板在光器件的应用进展 |

苏州联结科技有限公司执行董事谢斌教授 |

|

09:30-10:00 |

功率模块用AMB基板覆铜技术及性能研究 |

宁波江丰同芯半导体材料有限公司副总经理俞晓东 |

|

10:00-10:30 |

茶歇 |

|

|

10:30-11:00 |

高品级氮化铝粉末规模化制备及应用 |

厦门钜瓷科技有限公司技术副总监王月隆 |

|

11:00-11:30 |

薄膜沉积技术在基板制备中的应用 |

广东汇成真空科技股份有限公司项目经理覃志伟 |

|

11:30-12:00 |

高强韧陶瓷基板用高质量氮化物粉体的产业化制备及其应用 |

中国北方发动机研究所研究员吴晓明 |

|

12:00-13:30 |

午餐 |

|

|

13:30-14:00 |

引领高可靠氮化硅陶瓷覆铜基板在新能源汽车、光伏储能与工业功率模块的全域创新应用 |

南通威斯派尔半导体技术有限公司总经理周鑫 |

|

14:00-14:30 |

高端陶瓷封装基板金属化新技术与产业化进展 |

北大深圳研究院副教授吴忠振 |

|

14:30-15:00 |

低成本高可靠芯片空腔封装(ACC ACP): |

佛山市佛大华康科技有限公司高级工程师刘荣富 |

|

15:00-15:30 |

氧化铍基板新型金属化技术研究与应用 |

宜宾红星电子有限公司技术中心副主任陈超 |

|

15:30-16:00 |

茶歇 |

|

|

16:00-16:30 |

无钎焊料驱动:Si₃N₄和AlN陶瓷基板LAB技术对传统AMB的革新突破 |

哈尔滨工业大学(威海)特聘副研究员宋延宇 |

|

16:30-17:00 |

芯片陶瓷封装基板缺陷检测大模型关键技术与装备 |

东北大学软件学院教授 |

|

17:00-17:30 |

晶圆级金刚石高功率用芯片散热基板 |

中科粉研河南超硬材料有限公司董事长冯建伟 |

|

18:00-20:00 |

晚宴 |

|

邮箱:ab057@aibang.com

方式二:长按二维码扫码在线登记报名

https://www.aibang360.com/m/100241?ref=196271