本文来源于《数字时代》,侵权联系删除

FOPLP(扇出型面板级封装)是近来非常受瞩的先进封装技术。《日经亚洲》报导,传出台积电面板级装技术(Panel-level packaging,简称PLP)的开发已经进入尾声,这项技术将能够提高运算性能满足AI时代的新需求,被认为是封装领域迈向新技术的关键一步,预计2027年可以逐步进入量产阶段。

台积电此举不仅是技术上的突破,更意在为面板级封装设定行业标准,引导从设备制造商到材料供应商的整个芯片供应链进行调整,以适应方形基板的生产。

但FOPLP技术到底是什么? 为何市场传出台积电已订定以「方」代「圆」目标,甚至有它是「下一个CoWoS」的说法传出?针对FOPLP,《数字时代》以下为您解密产业关键词,并盘点FOPLP受惠台厂名单!

一、FOPLP为何是先进封装新希望?

AI热潮正夯! 而为发展如ChatGPT等大型语言模型(LLM),全球云端巨头无不广设数据中心,准妥「算力军火库」。 然而,要打造具备生猛效能的AI芯片,先进封装就是个中关键!

先进封装意味着将不同种类的芯片,包括逻辑芯片、存储器、射频芯片等,透过封装及堆叠技术整合在一起,以提升芯片性能、缩小尺寸、减少功耗。 例如,台积电针对7纳米制程以下的CoWoS技术,就是代表性的先进封装技术。

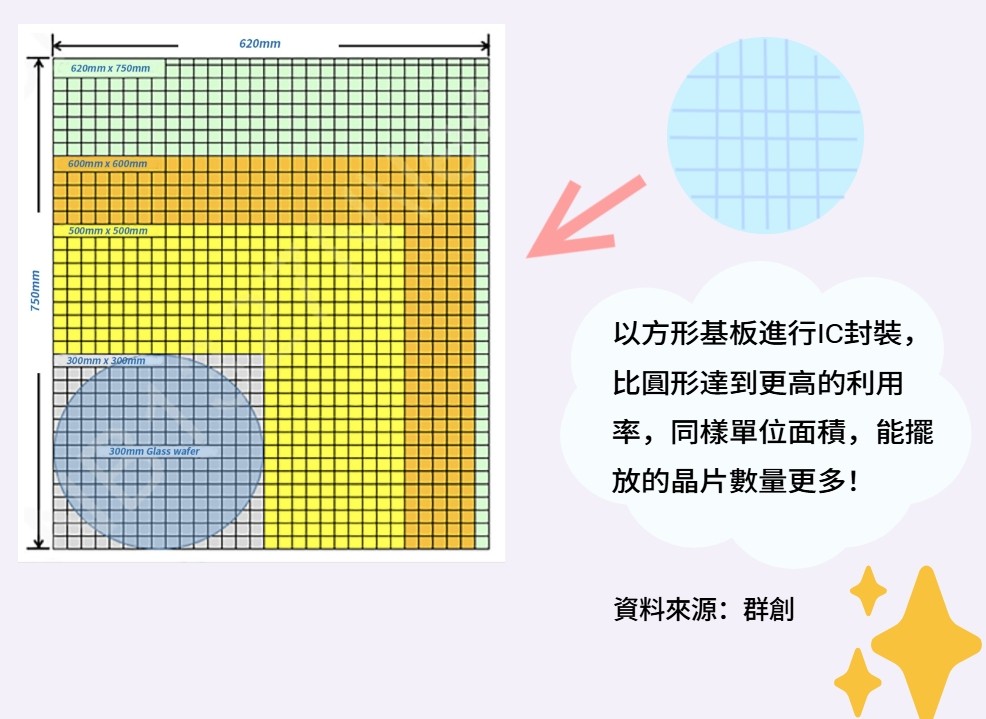

而FOPLP接棒台积电CoWoS备受关注的原因,在于透过「方形」基板进行IC封装,可使用面积可达「圆形」12吋晶圆的7倍之多,达到更高的利用率! 白话来说,就是同样单位面积下,能摆放的芯片数量更多。

FOPLP和CoWoS差在哪?

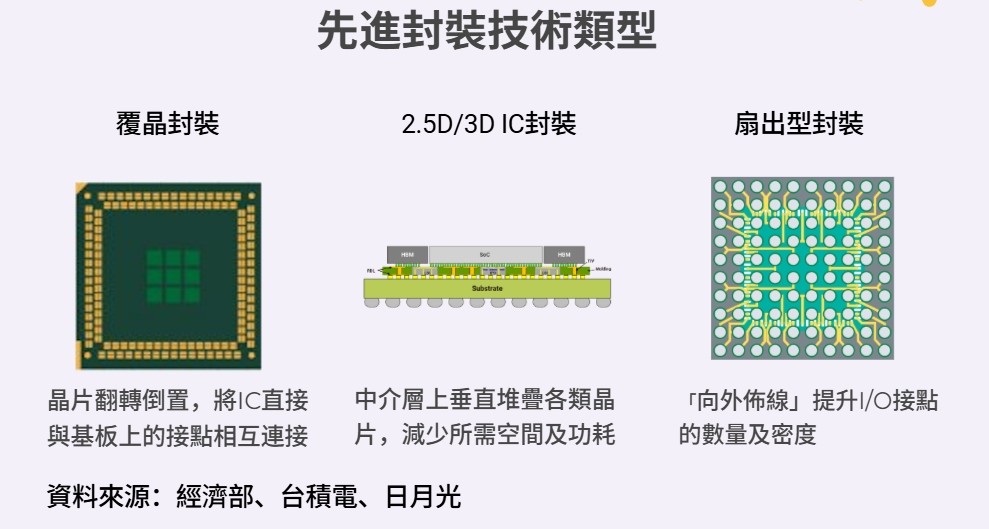

现阶段的先进封装技术可分为「覆晶封装」、「2.5D/3D IC封装」、「扇出型封装」等类型:

-「覆晶封装」(Flip-Chip)透过把芯片翻转倒置,将IC直接与基板上的接点相互连接;

-「2.5D/3D IC封装」在中间层上垂直堆叠各类芯片,由此缩小接点间距,减少所需空间及功耗, CoWoS便是属于此类 ;

-「扇出型封装」(Fan-Out Packaging)则是相对于「扇入型封装」(Fan-In Packaging),两者在芯片设计的重分布层(Redistribution Layer, RDL)布线方式有所不同,扇入型为向内布线,讯号输出及输入的「I/O接点」数量受到限制; 扇出型则是向内、向外布线皆可,从而提升I/O接点的数量及密度 。

扇出型封装可再细分为两种分支,分别是已投入应用多年的扇出型「晶圆级」封装(Fan-Out Wafer-Level Packaging, FOWLP),以及 本文主题的扇出型「面板级」封装(Fan-Out Panel-Level Packaging, FOPLP)。

垂直堆栈的CoWoS封装,目前主要运用在先进制程的AI运算芯片、AI服务器处理器的晶片封装,而FOPLP就各业者现阶段的描述,主要用于成熟制程为主的车用、物联网的电源管理IC等,两种封装技术的应用有所不同。