近日,电子信息与电气工程学院微纳电子学系周健军教授课题组在IEEE Journal of Solid-State Circuits(JSSC)上发表题为"A 60MS/s 5MHz-BW Noise-Shaping SAR ADC with Integrated Input Buffer Achieving 84.2dB-SNDR and 97.3dB-SFDR Using Dynamic Level-Shifting and ISI-Error Correction"的模数转换器(ADC)芯片研究成果。

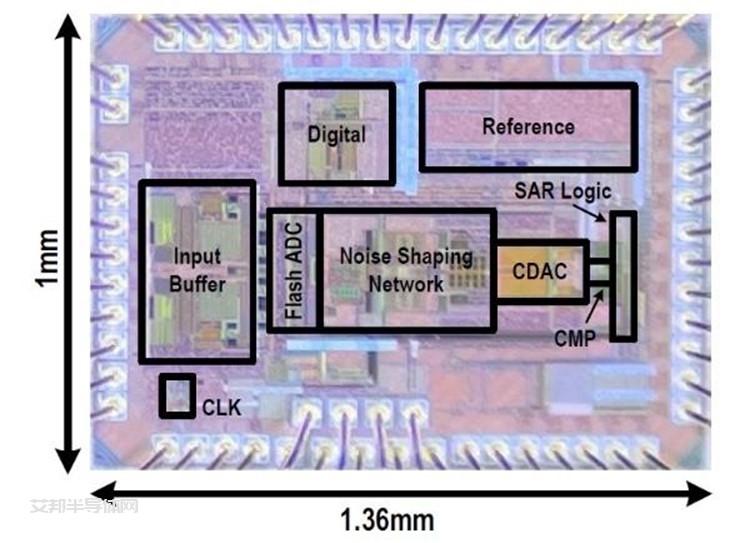

集成输入缓冲器的逐次逼近型ADC芯片照片

研究内容

该研究重点解决了ADC在系统应用中面临的集成输入缓冲器时的设计挑战,揭示了ADC符号间串扰的产生机理以及对ADC精度的影响,文章提出动态电平移位技术与采样误差校正技术,从而实现了片上集成缓冲器的高性能ADC的线性度提升。

ADC芯片采用CMOS工艺流片验证,在采样率为60MS/s带宽为5MHz时,实现了84.2dB的SNDR和97.3dB的SFDR,达到了截止论文投稿时文献报道的集成了输入缓冲器的逐次逼近型ADC的最好优值指标(FoMw为60.6 fJ/conv.-step,FoMs为172.1dB)。此外,该芯片在设计时采用了多项数字辅助校准技术,并考虑了ESD保护等芯片可靠性问题。

论文链接:https://ieeexplore.ieee.org/document/9810848

文章俩月:上海交通大学