人工智能 (AI) 已成为创新和进步的重要催化剂。对 AI 计算能力日益增长的需求,推动了异构集成向更大封装尺寸发展,从而引发了人们对扇出型面板级封装 (FOPLP) 技术日益增长的兴趣。本文探讨了日月光 (ASE) 在该领域的实践和发展,深入探讨了塑造行业未来的技术复杂性和新兴趋势。艾邦建有半导体先进封装之FOPLP交流群,欢迎大家申请加入。

AI/HPC 的先进封装

专为人工智能和高性能计算 (HPC) 应用设计的先进封装架构,将内存放置在靠近人工智能处理器(例如 GPU 和 AI ASIC)的公共中介层上,而不是将它们分别放置在印刷电路板 (PCB) 上。这种配置缩短了内存和 ASIC 之间的距离,从而实现了更快的速度、更大的带宽和更大的容量,最终提升了整体计算能力。

随着计算能力需求的增长,中介层需要以并排配置的方式容纳更多芯片,从而导致尺寸增大。目前,ASE 已实现三倍光罩尺寸的中介层,但未来的需求趋势是更大的尺寸,例如 3.5 倍、4.5 倍和 5.5 倍。5.5 倍光罩尺寸的中介层约为 60 毫米 x 70 毫米,超过了当今量产封装基板的尺寸。

面板级封装工艺的优势

在生产小尺寸中介层时,面板工艺的优势似乎有限。然而,随着中介层尺寸的增大,其优势将更加明显。具体而言,晶圆加工中圆形基板的利用率会随着中介层尺寸的增大而下降,因为边缘芯片占用更多空间,导致切割后材料浪费加剧。例如,一块12英寸(300毫米)晶圆只能容纳9个尺寸为5.5倍光罩尺寸的中介层。相比之下,一块300毫米面板可以容纳16个相同尺寸的中介层。这意味着从晶圆到面板的转换效率显著提升(1.78倍)。总而言之,对于芯片集成中使用的大型中介层(大于3倍光罩尺寸),面板工艺的性能明显优于晶圆工艺。

面向AI/HPC的扇出型封装技术

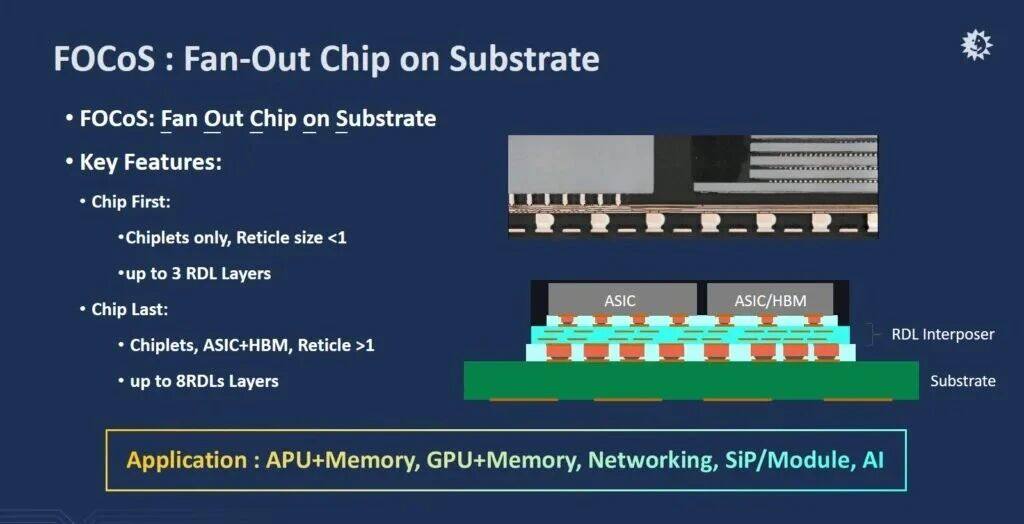

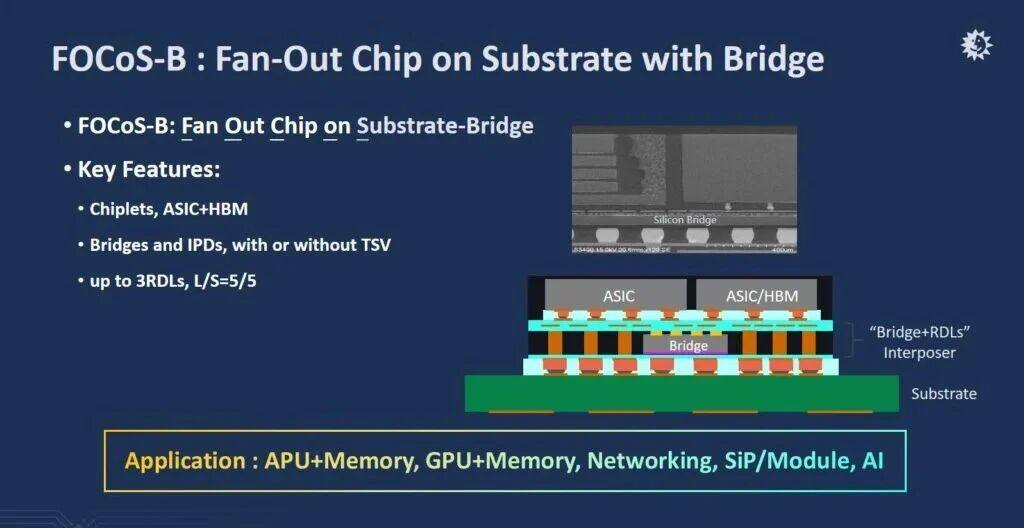

目前,用于集成 AI 芯片(例如 GPU 和内存)的先进封装技术主要包括两个平台:硅中介层 (Si interposer) 和有机中介层 (Organic interposer)。将芯片放置在硅中介层上进行功能集成的方法称为 2.5D 封装。相比之下,有机中介层利用重分布层 (RDL) 进行功能集成,称为 FOCoS(扇出型芯片基板)封装。如果在 RDL 中介层内加入桥接结构,则称为 FOCoS-Bridge。

FOCoS:先芯片还是后芯片

FOCoS 主要有两种方法:先芯片(Chip First)和后芯片(Chip Last)。先芯片方法主要用于封装和集成小型芯片。该工艺首先将芯片放置在载体上,然后进行模塑,最后添加重分布层 (RDL)。通常,不建议使用先芯片工艺集成过多芯片,通常限制在两到三个芯片左右。此外,整个中介层的光罩尺寸不建议过大(通常小于光罩尺寸的 1 倍),并且通常需要 2 到 3 层 RDL。

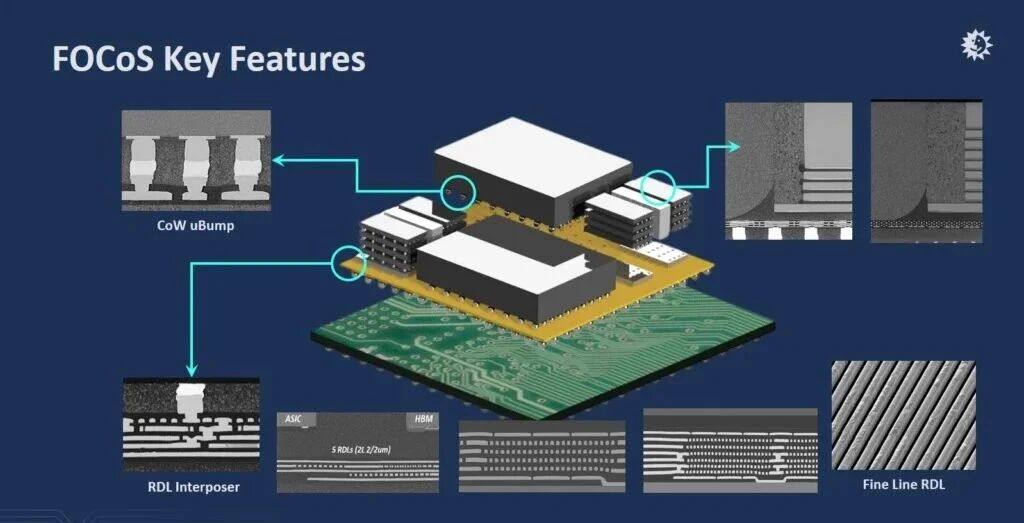

目前,高性能计算 (HPC) 和人工智能 (AI) 应用中 ASIC 和高带宽存储器 (HBM) 的集成主要采用 Chip Last 解决方案。该方案需要在载体上制备 RDL 中介层,然后将芯片放置到 RDL 中介层上进行连接。通常,Chip Last RDL 中介层的光罩尺寸相对较大(> 1 倍光罩尺寸),未来可能需要多达 9 层 RDL,其中包括至少 7 层细线,线宽/线距 (L/S) 可达到 2/2μm。

FOCoS 的主要挑战

随着半导体技术的进步,顶层芯片ASIC的μBump间距已从55μm逐渐减小到40μm,未来可能进一步缩小到25-30μm。这种减小给封装工艺带来了越来越大的挑战。此外,为了满足日益增长的AI算力需求,HBM集成已从四层发展到八层甚至十二层内存堆栈。中介层上ASIC周围的HBM数量也在不断增加,目前的趋势是4个或8个HBM,未来计划目标是12个甚至20个。随着集成的芯片数量不断增加,中介层的尺寸也越来越大。

通常,RDL 中介层需要两层 2/2μm 细线来实现 ASIC 与 HBM2/2E 之间的通信,而 HBM3/3E 则需要四层 2/2μm 细线,HBM4/4E 则可能需要 8 层 RDL,其中包含 6 层细线。在某些设计中,可能需要 8 层 2/2μm 细线才能有效地将这些存储器组件与先进的 ASIC 芯片集成,从而实现最佳通信。

FOCoS-Bridge的技术趋势

FOCoS-Bridge 技术利用硅桥 (Silicon Bridge) 为芯片互连提供精细线路 (L/S<0.5/0.5μm)。因此,FOCoS-Bridge 中介层上 RDL 的布线密度要求低于 FOCoS 中介层,L/S 至少只需达到 5/5 μm。硅桥通常在台积电 (TSMC)、联华电子 (UMC) 或格芯 (GlobalFoundries) 等代工厂制造。

为了应对日益复杂的芯片集成,FOCoS-Bridge 技术利用硅桥实现芯片间的高布线密度互连,同时在中介层上提供宽间距 RDL 层以传输电源和信号,从而增强设计灵活性。该技术还可以在 ASIC 芯片下方集成其他组件,例如独立的集成无源器件 (IPD),以增强电源完整性 (PI) 和信号完整性 (SI)。

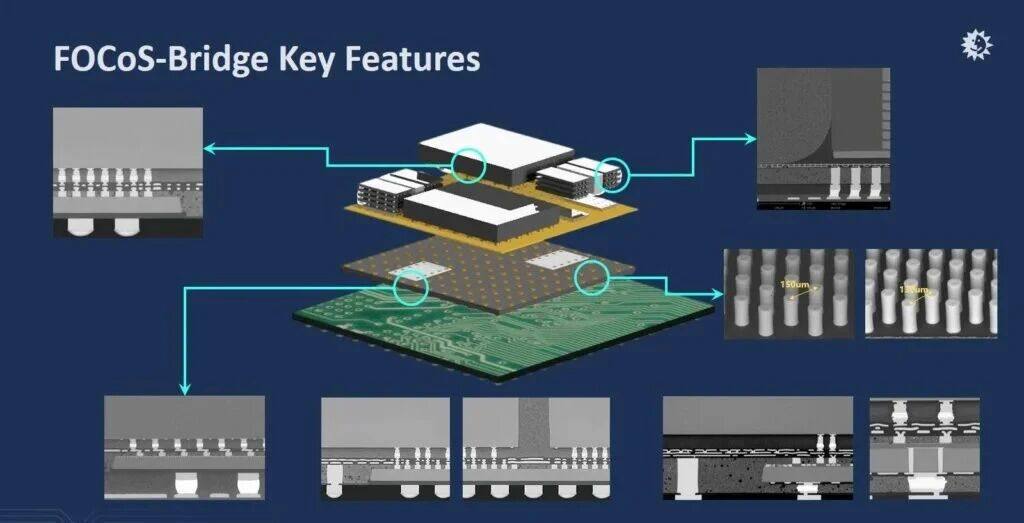

FOCoS-Bridge 的主要挑战

FOCoS-Bridge 技术需要在桥接芯片周围设置许多高大的铜柱(如下图所示),以实现垂直连接。为了满足日益增长的垂直连接需求,这些铜柱之间的间距已从 150 μm 缩小至约 130 μm。

随着 FOCoS-Bridge 技术日益复杂,未来的桥接芯片将需要集成类似于 2.5D 封装 Si 中介层中使用的硅通孔 (TSV),以提供更高效的垂直供电路径。此外,随着 HPC 供电要求日益复杂,将深沟槽电容器 (DTC) 集成到 FOCoS-Bridge 中介层中以支持更佳的 PI/SI 信号通信至关重要。

扇出型 PLP 开发

日月光正在开发一条采用 310×310 毫米面板的自动化生产线。虽然更大的面板尺寸更具成本效益,但也带来了更大的制造挑战。为了解决这个问题,日月光从较小的面板入手,开发用于先进 AI 和 HPC 封装的 FOPLP 工艺,并计划将其扩展到 600×600 毫米面板。

FOCoS-Bridge TV的面板工艺挑战

下图所示的测试载体(电视)是在300×300毫米的面板上制作的。虽然该工艺与之前介绍的FOCoS-Bridge技术类似,但由于从晶圆(圆形)工艺过渡到面板(方形)工艺,存在显著的技术差异。例如,晶圆加工中常用的旋涂工艺无法直接应用于面板加工,需要改为狭缝涂布,材料也需要进行调整。此外,用于集成AI芯片的中介层通常大于单个曝光场,在目前的晶圆光刻工艺中需要进行多掩模版拼接。因此,激光直接成像(LDI)等无掩模版曝光技术应运而生,它们能够显著提升生产效率,并可通过软件设置灵活补偿,不受掩模版的限制。

FOCoS-Bridge TV的主要制造步骤如下:

(a)在面板上形成高柱后,放置桥接芯片 (Bridge Die),然后进行成型和研磨。桥接芯片的精确放置至关重要;否则,第一层介电层(PI 钝化层,研磨后形成)的通孔将难以与桥接芯片上的铜柱 (Cu Studs) 精确对齐。由于顶部芯片 (Top Die) 的微凸块间距 (Micro Bump Pitch) 已缩小至约 35μm 至 40μm,因此铜柱 (Cu Studs) 可能仅形成 20μm,而 PI 通孔可能小至 10 至 15μm。

(b)在成型产品上形成多层 RDL 和 μBump 焊盘,以完成扇出型中介层结构。关键技术挑战包括实现狭缝涂层的均匀性、光刻的精确性以及电镀过程中镀层厚度的控制。

(c)然后将AI芯片连接到中介层上,中介层的尺寸大约是光罩的三倍,接近50mm x 50mm。最后,在应用底部填充和成型后,移除载体,并在中介层背面形成可控塌陷芯片连接(C4)凸块。

未来展望

鉴于这些挑战的复杂性,ASE 认识到独立实现 FOPLP 极具挑战性。与设备制造商、材料供应商和自动化供应商的合作至关重要。在这个快速发展的领域,半导体封装技术的每一次进步都开启了新的可能性。我们可以携手利用 FOPLP,共同书写半导体行业下一个辉煌篇章。

艾邦建有半导体先进封装之FOPLP交流群,欢迎大家申请加入。

包括但不仅限于以下议题

| 序号 | 议题 |

|---|---|

| 1 | TGV玻璃核心技术的挑战与解决方案 |

| 2 | 玻璃基板先进封装技术发展与展望 |

| 3 | 三维封装硅通孔与玻璃通孔技术发展及应用 |

| 4 | 先进封装对玻璃基板基材的要求 |

| 5 | 无机玻璃材料的本构模型、破坏机理及其在工程中的应用 |

| 6 | 玻璃基互连技术助力先进封装产业升级 |

| 7 | 真空镀膜设备在玻璃基板生产加工中的关键作用 |

| 8 | 玻璃芯板及玻璃封装基板技术 |

| 9 | 玻璃通孔结构控制、电磁特性与应用 |

| 10 | 玻璃基板及先进封装技术研究与应用 |

| 11 | 如何打造产化的玻璃基板供应链 |

| 12 | 电镀设备在玻璃基板封装中的关键作用 |

| 13 | 玻璃基FCBGA封装基板 |

| 14 | 显微镜在半导体先进封装缺陷检测中的应用 |

| 15 | 激光系统应用于TGV制程发展 |

| 16 | Panel level激光诱导蚀刻 & AOI |

| 17 | 利用激光诱导深度刻蚀技术实现集成多种功能结构玻璃基板加工 |

| 18 | FLEE-TGV助力先进封装玻璃基板发展 |

| 19 | 在玻璃基板上开发湿化学铜金属化工艺 |

| 20 | 异构封装中金属化互联面临的挑战 |

| 21 | 电化学沉积法制备TGV-3D互连结构 |

| 22 | 高效RDL制造技术:赋能多种互联结构的面板级封装 |

| 23 | TGV金属线路制作的工艺难点及技术解决路径 |

| 24 | 玻璃基光子解键合技术 |

| 25 | 基板积层胶膜材料 |

| 26 | 面向先进封装的磨划解决方案 |

| 27 | 多物理场仿真技术在玻璃基先进封装中的应用 |

| 28 | 玻璃基片上集成无源 |

| 29 | 基于TGV的高性能IPD设计开发及应用 |

| 30 | 下一代ABF载板-玻璃基及其潜在的机遇与挑战 |

| 31 | 面板级键合技术在FOPLP中的应用 |

更多相关议题征集中,演讲及赞助请联系李小姐:18823755657(同微信)

报名方式一:扫码添加微信,咨询会议详情

李小姐:18823755657(同微信)

邮箱:lirongrong@aibang.com

注意:每位参会者均需要提供信息

方式二:长按二维码扫码在线登记报名

或者复制网址到浏览器后,微信注册报名

https://www.aibang360.com/m/100272

阅读原文,点击报名