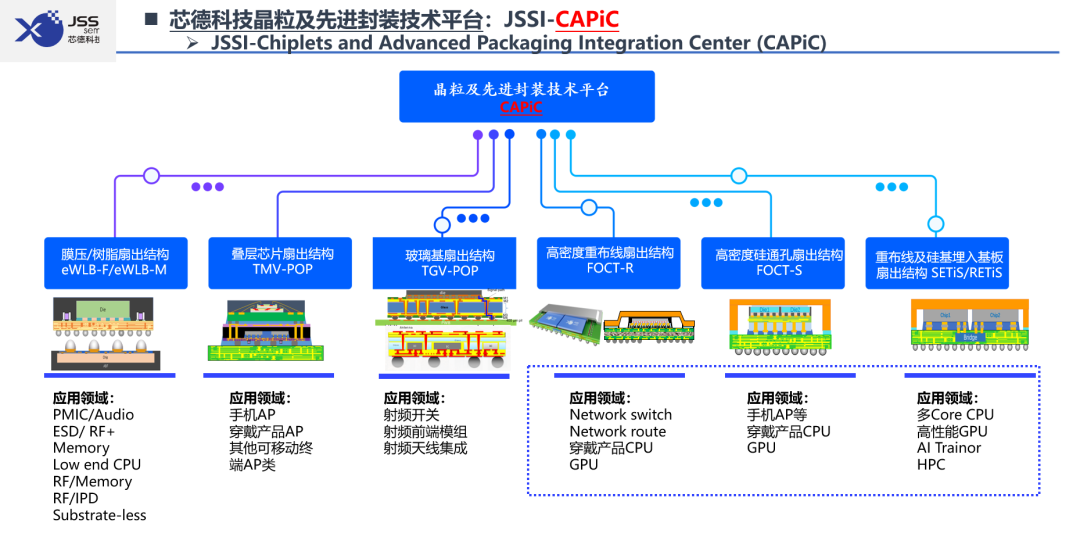

2023年3月10日,芯德科技在业界推出了“CAPiC晶粒及先进封装技术平台发布会”,芯德科技把多种扇出型封装技术进行了全方位的技术规划,从而为客户带来更多的封装技术选择。CAPiC, 全称为Chiplet and Advanced Package integration Center, 这里面包括6种封装技术规划集成电路领域核心的应用包括HPC-高性能运算、AI-人工智能、BD-大数据等的算力的急剧要求对集成电路高端封装也起到了进一步的核心推进本文先对这六种技术进行了技术解释,然后着重对FOCT-R即FANOUT-Connected Tech-RDL 进行全面的技术背景分析,最后阐述了FOCT-R为客户带来的更多的技术方案选择。

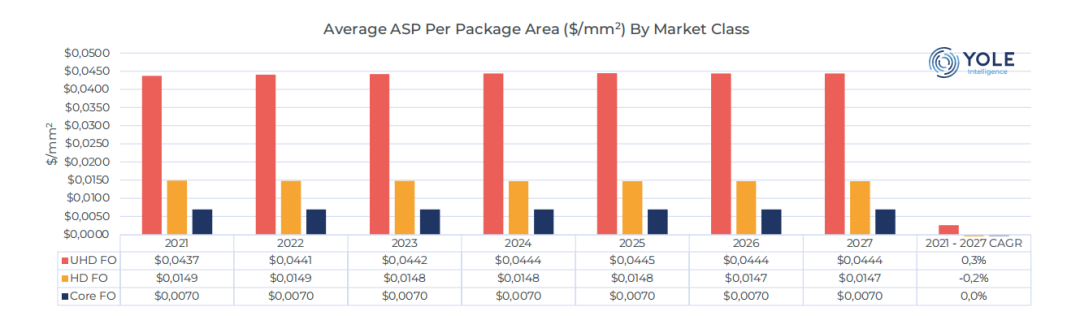

世界范围类FANOUT/2.5D/3D 市场分析, 2021/1Q 世界半导体协会根据封装技术的发展,再次一致更新了半导体先进封装的技术定义,用于统一世界范围内各种协会的数据统计基础,先进封装定义:SiP (WB/FC/SMT- Mix Hybrid), FCCSP, FCBGA, 2.5D/3D, WLCSP, FANOUT 为先进封装统计范畴。根据2022/2Q最新预测,2021~2027年,先进封装CAGR(Compound Annual Growing Rate 年度复合增长) 达到9.81%, 从337亿美金(2021 33.7B USD)成长到591亿美金(2027 59.1B USD)。先进封装技术使用的核心应用包括:5G/6G Communication, Automotive Infotainment/ADAS, data center, wearable devices; 先进封装技术范畴CAGA 本别是:2.5D/3D 13.73%, FCCSP 11.63%, FAN-OUT 11.16%, FCBGA 7.82%, SiP 4.30%, WLCSP 3.24%。其中,因为Mobile/Wearable device Marketing的放缓发展,WLCSP的增长CAGA明显放慢。特别对于FANOUT领域,业界进行了界定和分类:Core-Fanout, Core-FO, 对应的是芯德科技的eWLB-F& e-WLB-M 这两个平台,目前最大的Manufacturer集中在ASE/SPIL、Amkor、JCET 等几家。High-Density Fanout PKG, HDFO, 目前世界范围内集中在几个产品使用,包括Apple mobile APUs, Samsung Smartwatch APUs, Huawei-HiSilicon mobile/server APU/CPU;另外包括Qualcomm, Mediatek, ZTE等 芯片设计公司也在开始使用该技术平台,预计在2023/2024 flagship phone旗舰机上宣布实际使用。Ultra High density fan-out, UHD-FO,主要应用于AI,Networking 以及 HPC 高性能计算领域,广泛使用的目前包括ASE FOCoS, TSMC InFO series. 这里面HDFO/UHD-FO 业界部分的定义列入到2.5D/3D 领域,有一定的交叉性。综合市场分析 (包括所有的FANOUT以及3D 封装),Revenue 预计(USD):2022/12.4B, 2023/14.3B, 2024/16.5B, 2025/18.7B, 2026/20.2B, 2027/22B。所有的数据分析标明,采用该系列技术平台的产品会快速增长,到2027年,达到220亿美金的市场规模,注 2021最终营收105亿美金,其中TSMC占46亿美金。2021 FANOUT PKG Revenue 市场份额,TSMC 69%,ASE/SPIL 20%, JCET(including joint company) 4%, Amkor 3%, Nepes 2%, Samsung 1%,PTI 1%, Huatian 1%。据2021数据, FANOUT 技术:UHD FO 占47%,HD FO占33%,Core-FO 20% 。 Yole, Advanced Package Market Monitor, 2022/Q2 Data 芯德科技全面布局这些高技术含量的高端封装领域,包括LDFO ( Core FO), HDFO, UHDFO 等核心范畴。在HDFO/UHDFO方面, 公司在2023/4月份拿到了第一份工程研发批次的设计以及加工合同,为一家HPC客户提供超高密度的扇出型封装技术开发以及样品制作,目前该项目已经完成了设计以及电性仿真工作;在产业化方面,芯德科技预期在2024 能够实现HDFO/UHDFO等技术的全面产业化工作,达成实际的销售产值。另外在LDFO方面,公司已经实现了规模化量产,产品应用包括射频芯片、毫米波雷达芯片、毫米波高清传输芯片、音频解码芯片、EEPROM&LENS Driver 芯片、PMIC电源管理芯片等等,2023年总计出货量超过4000万颗,特别的是,公司自主研发的拥有核心专利的超薄型Wafer level Fanout 即QFN-Like技术,实现了0.23 厚度四方平面封装外形,得到了数家设计公司的技术认可,已经进入了产业化阶段,全面进入市场。

芯德科技这次的技术规划里面,涵盖了包括RDL- Organic Base Interposer、Glass-Interposer、Silicon-Interposer三种核心的转接板解决方案;还包括了RDL Base和Silicon Base的嵌入式解决方案;同时,适用于电源类和毫米波类产品的低IO扇出型封装解决方案也在其中。接下来简述这6种解决方案: (一) FOCT-R (Fanout Connected Tech-RDL),主要应用在数据中心,服务器CPU,推算AI, IOT芯片,实现了同质,异质芯片间的互连,可以整合两种具有不同特点的基板:高层数的基板,更精密的再布线转接板(RDL Interposer),可以进一步实现更大的2.5D封装,并降低基板层数。使用再布线和凸块技术,实现最小2μm的线宽,2um线间距的布线。同时,芯德科技推出单芯片FOCT-R 技术,采用Interposer 来有效降低基板的制造层数。 (二) FOCT-S (Fanout Connected Tech- S),专用于需要高性能和大面积封装技术的高性能计算(HPC)、人工智能(AI)、数据中心和网络产品等领域,使用硅转接板(Si Interposer),可以实现更高精度(<1um 线宽和间距)的再布线层,实现更高密度的连接,提供更高性能,充分发挥2.5D封装的优势和特点eWLB-M,主要应用于中、大颗芯片的扇出型封装,封装尺寸能够在8x8~15x15mm 左右,使用再布线和凸块技术,可以直接连接芯片与芯片,减少厚度,减少连接损耗,降低成本,高性价比,可应用于毫米波,射频和无线芯片的封装,处理器和基带芯片封装; (三) SETiS/RETiS (Silicon Embedded Tech in Substrate/ RDL Embedded Tech in Substrate), 嵌入式多芯片互连桥接,可以实现异质和同质芯片的互联,成本更低,实现包括CPU、图形卡、内存、IO及其它多个芯片间的通信,通过将再布线层转接板(RDL Interposer)嵌入到基板中可以实现在不增加封装厚度的前提下,提高芯片间的通信效率,降低损耗,降低基板设计难度和层数。 (四) TMV-POP,主要应用在高算力的封装,通过将再布线转接板将同质或者异质芯片进行互联后并通过高铜柱和塑封料的将互联部分引入封装体的背面并进行引出凸点,进行再次与另一封装体进行互联,在不增加封装平面尺寸的前提下,实现封装体与封装体的互联,提供性能,并充分发挥不同封装体的优势。 (五) TGV-POP,主要应用在射频类的芯片封装,具有高密度、低翘曲(CTE match)、高可靠性、低损耗因子、低芯片偏移、低翘曲等优点,该封装利用玻璃绝缘体材料,使得衬底损耗和寄生效应大大减小,保证了传输信号的完整性,在玻璃上进行再布线,转移凸点并在此基础上,芯片与芯片间的封装互联,充分满足高频信号传输的需求; (六) eWLB-F& eWLB-M,主要应用于小颗芯片的扇出型封装,封装尺寸能够在0.6x0.6~15X15mm 左右,使用精细化的ABF膜 以及晶圆级的模封方案,再布线和凸块技术,将芯片进行最高效的封装和保护,也可以多颗芯片互联,实现最小封装尺寸,降低成本,高性价比,可用于模拟芯片,音频播放,电压保护的等芯片,该方案可以有效取代部分的基板制造需求,实现从FCCSP 到 FANOUT-CSP的转化。

对于FOCT-R的技术,该文将从技术背景、行业发展情况、芯德科技的核心方案等几个方面进行全方位的阐述,以方便广大先进封装从业人员的深度理解以及客户端的设计采用等等。在这里面,我们又会提及到摩尔定律, 大家知道,美国英特尔公司是有诺伊斯,戈登·摩尔,安迪·格鲁夫三位科学家创立,而业界熟知的摩尔定律就是由戈登·摩尔提出,核心原文是:“The number of transistors incorporated in a chip will approximately double every 24 moths;It may prove to be more economical to build large systems out of smaller functions which are separately packaged and interconnected,大家熟知的内容为:集成电路上可以容纳的晶体管数目在大约每经过18个月到24个月便会增加一倍。换言之,处理器的性能大约每两年翻一倍,同时价格不变,即单个晶体管的价格下降为之前的一半;摩尔定律的后半部分,直到最近几年才被人理解,意思是大的芯片系统为在发展到一定程度后,把核心模块分开并且通过封装的形式来实现会是一种比较经济可行的方式。

在芯片发展到28nm制程能力之后,集成电路产业界遇到了一些核心的问题,这里面包括技术瓶颈以及成本方面的瓶颈,这些瓶颈的出现推动了先进封装技术的进一步的发展。

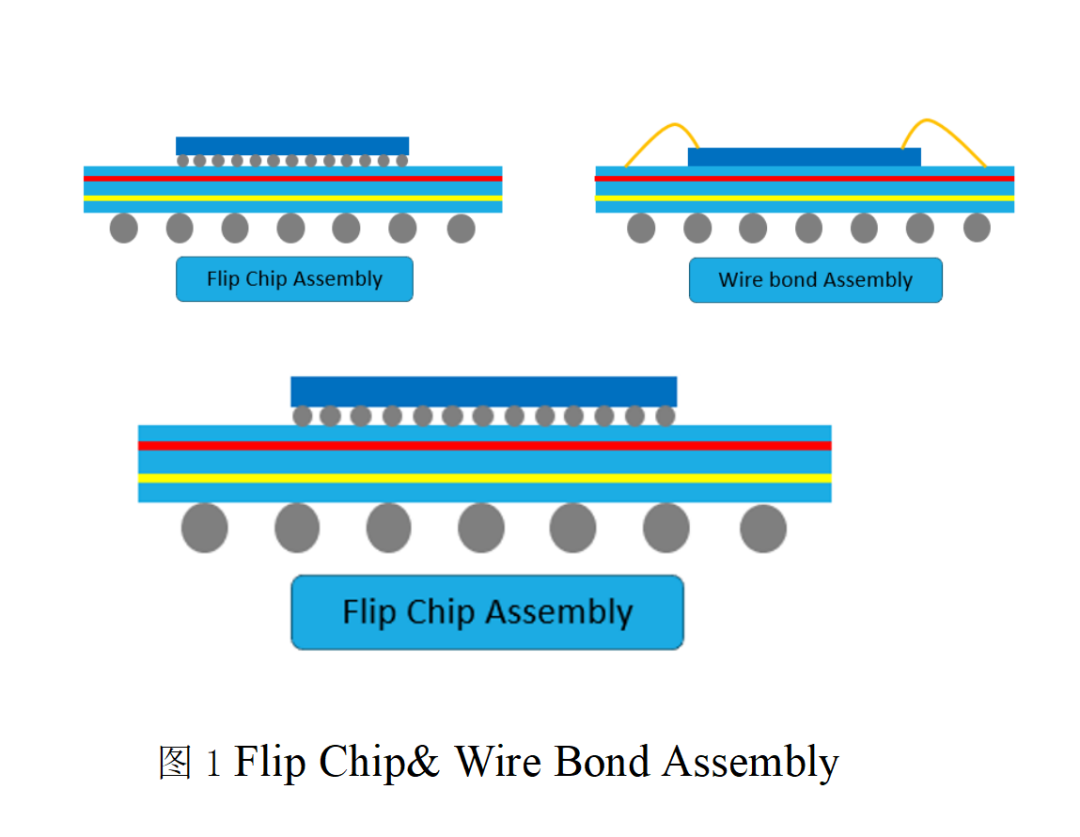

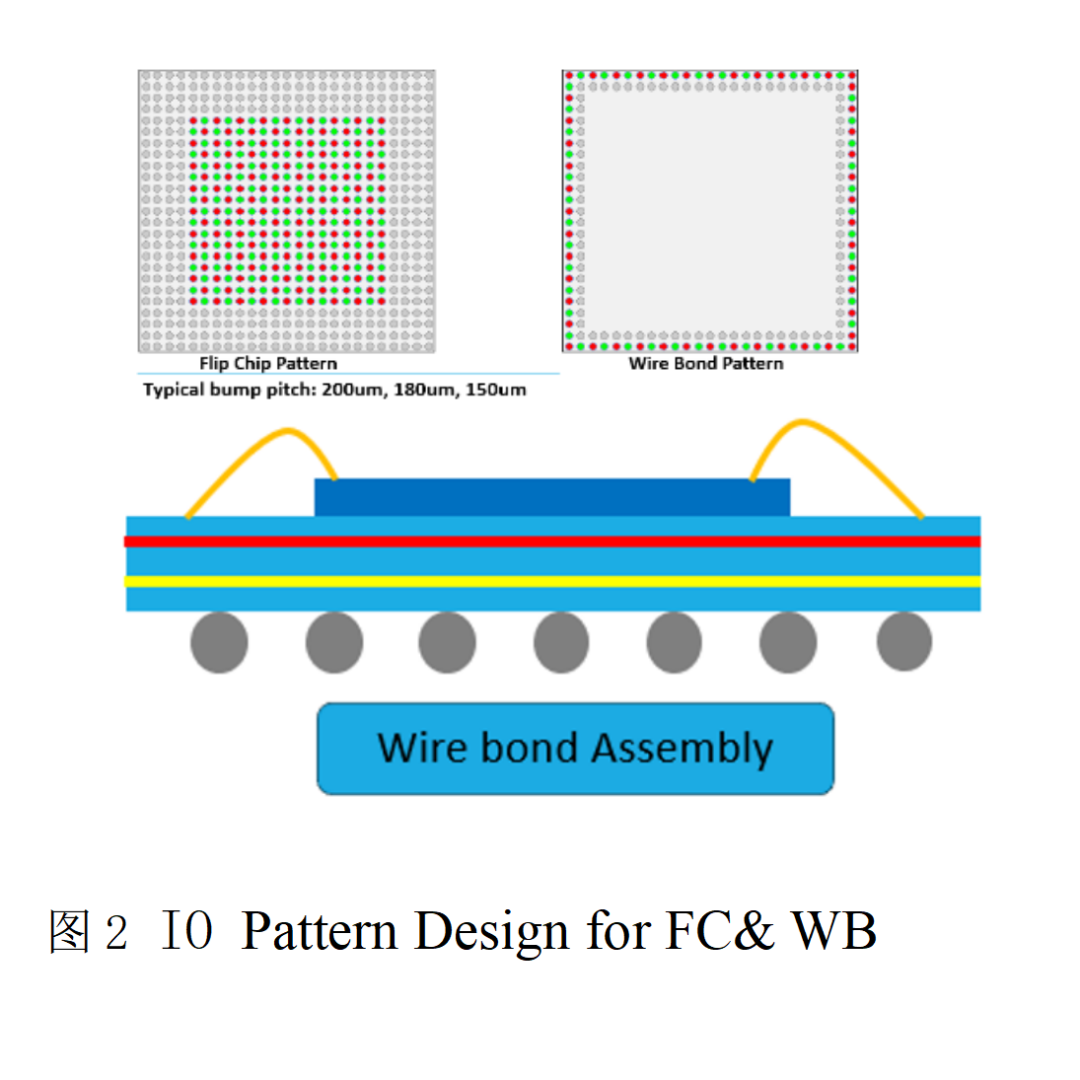

第一个技术瓶颈:超高先进的晶圆制程带来了更高的晶体管密度,实现了超小间距超高密度IO的晶圆制作;原来的封装技术无法满足客户对于更到IO的产品需求。业界原来主要通过Wire Bond 和Flip Chip 两种封装技术来实现芯片功能与周围环境系统的互连,如下图1&2 所示:

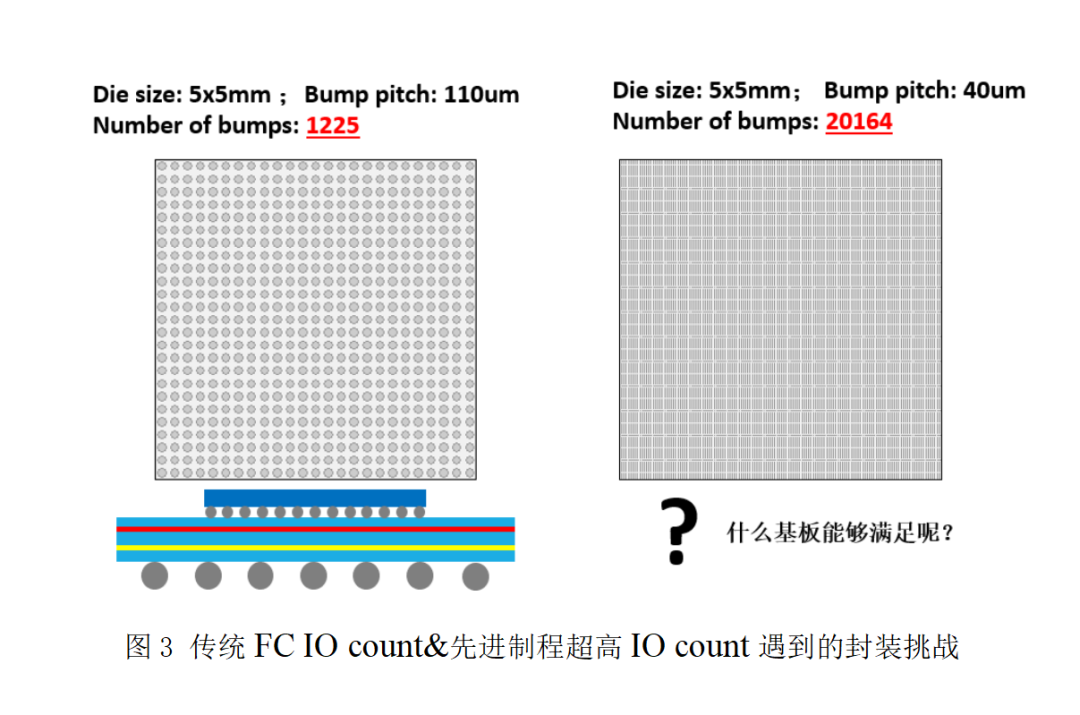

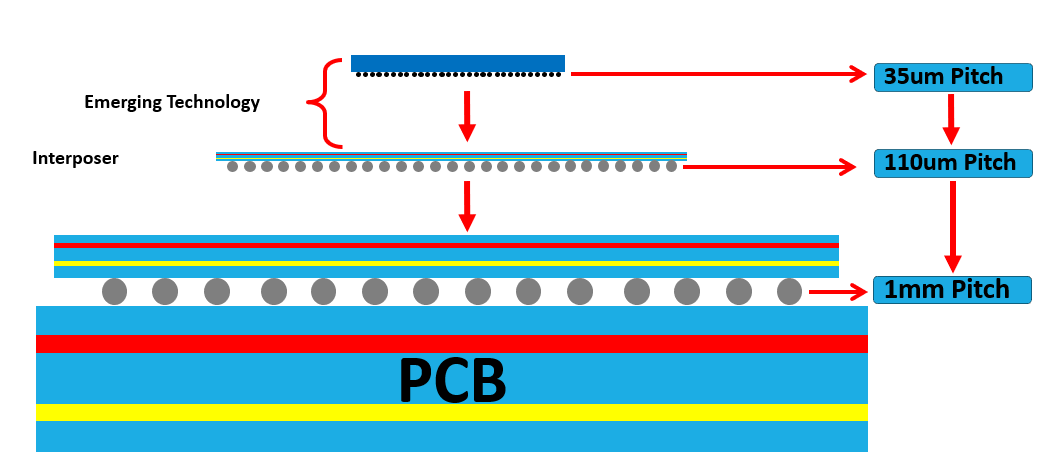

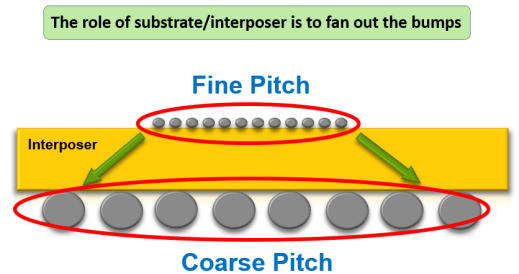

在传统的FC制程中,芯片IO Pitch 也就是对应的凸块Pitch的工艺能力在 110~200um 能力范围之类,以5X5 Die Size 为范例,IO的数量最多在1220 Pin Count, 这种110~200um的Pitch 受制于三个方面的制程:晶圆本身的制造能力、凸块制程能力、后道有机基板的制造能力。随着近几年技术的发展,晶圆制程以及凸块制程已经得到了极度的改善,Pitch 已经可以完成最小30~45um 的制程能力。核心的问题集中在有机基板上,现有的基板制造能力无法满足~40um Pitch的芯片IO输出设计,如图3所示:

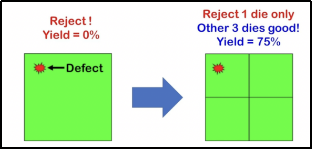

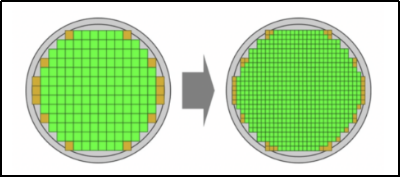

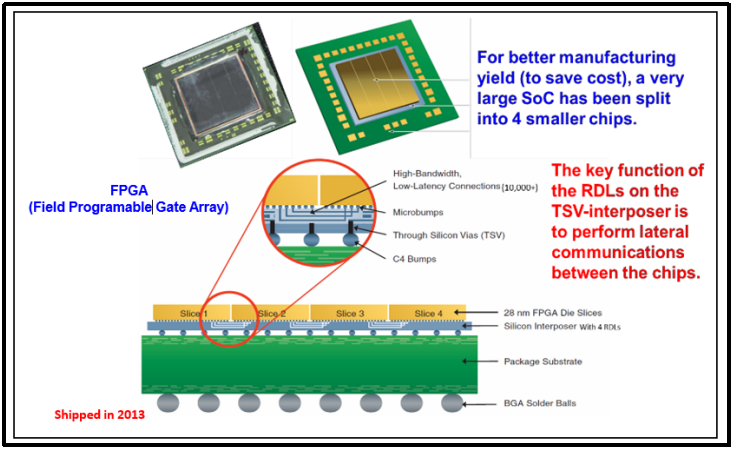

第二技术瓶颈, 由于芯片尺寸变大带来的晶圆工艺良率限制和影响越来越明显,这里面包括两个方面,一是晶圆制造制程本身带来的良率损失,在大芯片的制程中,良率损失非常的明显;二是由于芯片尺寸变大,Layout造成晶圆周边的无效空间变大造成的损失。2011年,Xilinx 开发了Virtex-7 HT Family 服务器芯片,采用技术 TSMC,28nm, SOC Design, FCBGA Package. TSMC当时遇到了巨大的良率问题,因为芯片尺寸过大,良率在52% 水准。2012 年,Xilinx改变了设计方案:TSMC,28nm, CHIPLET Design, into 4 CHIPLETS& TSMC , CoWoS-S PKG, TSV RDL Pitch 0.4um,采用65nm Silicon Interposer 技术;2013年10 月,Xilinx&TSMC Announcement: 出货了世界首颗量产的异质封装PKG 芯片,打开了2.5 D 封装的技术先河。 对于良率的影响的理解,具体的可以参考如下的图示:

图4 大芯片尺寸带来的良率影响VS分割小芯片带来的影响;Virtex-7 HT family 多芯片互联芯片

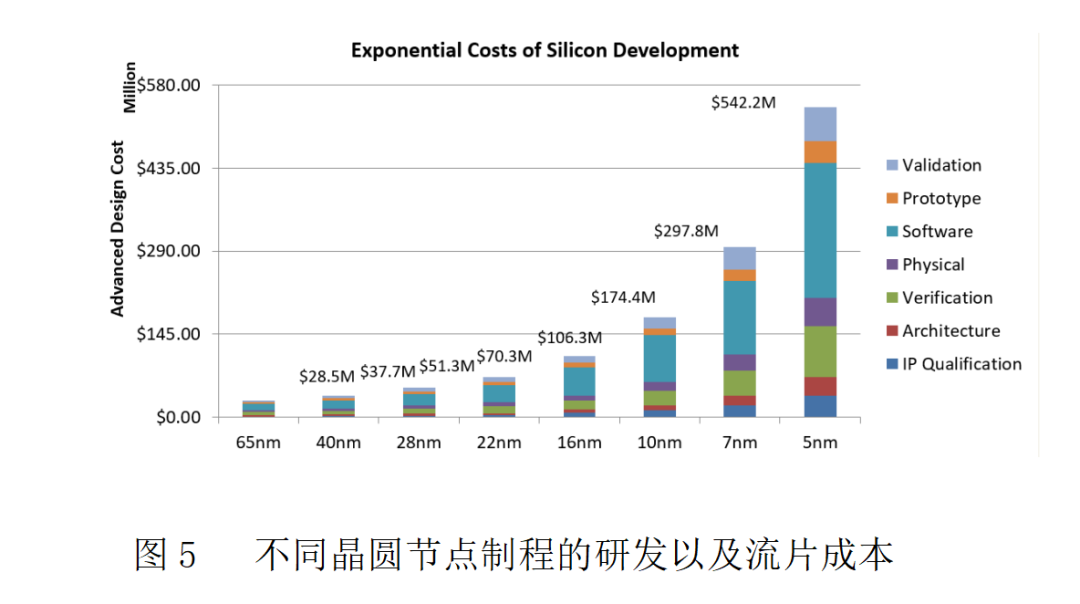

另外,对于成本方面的瓶颈这个也是非常的明显,主要表现在超先进制程开发的成本以及制造成本非常巨大,造成本身超先进制程产能严重受限,以及设计公司NPI的成本超高。以16纳米制程为分水岭来看,开发16纳米制程的新品成本在1.1亿美金数量级,到了5nm 制程,NPI的流片成本包括软件以及硬件成本在5.5亿美金,一般设计公司需要巨大财务支持才能推进。

在这些技术和经济瓶颈的双重影响下,芯德科技研发团队推出FOCT-R的技术,为客户全面解决这些问题提供了方案,这里面包括单芯片的超高密度扇出、异质结构的多芯片超高密度扇出型互联、同质结构的多芯片超高密度扇出型互联封装技术。

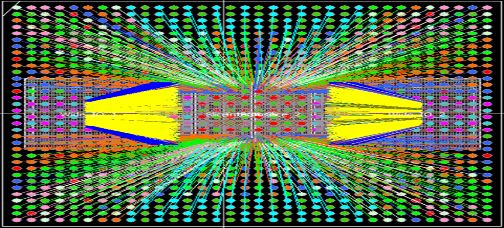

第一种技术方案:FOCT-R-Single Chip High density fanout 技术,该技术的核心是interposer-转接板的设计以及工艺制作,芯德采用的晶圆级工艺来实现超高密度的转接板制作,从而实现了 Pitch 35~40um FC 到 110um pitch Interposer 上,然后再通过多制程后FC到传统的1mm Pitch有机载板上面。该方案解决了核心技术瓶颈问题的同时,也有效的降低了底层有机载板的设计以及工艺制造难度。芯德科技已经和数个客户展开了产品评估以及前期的设计工作,核心技术数据:Chip size: 8X8mm, Micro Bump pitch:40um, IO: ~18000, Interposer: 8 layers with 4P/4M design, Min RDL W/S: 4um, C4 Bump Pitch: 110um, Substrate: 4-2-4 layers with thickness, OSP pad, 1mm BGA Ball pitch;产品应用为业界需求比较强劲的HPC-High Performance Computing 芯片的应用。

图6 Core Concept: JSSI-FOCT-R Single Chip High density fanout

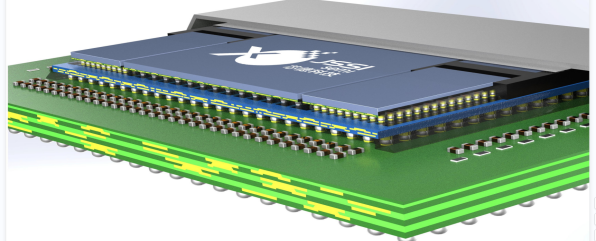

第二种技术方案:FOCT-R-Homogeneous Chips High Density Fanout Integration/同质芯片超高密度扇出型互联技术, 该技术可以将相同制程的高密度芯片帮助实现超高密度的互联,从而实现客户对于PPA-Power,Performance,Area 的高要求。芯德科技已经和国内外数家客户展开了产品设计仿真、Interposer 工艺流程制定、样品制作以及测试等核心工作。

图7 Core Concept: FOCT-R-Homogeneous Chips High Density Fanout Integration

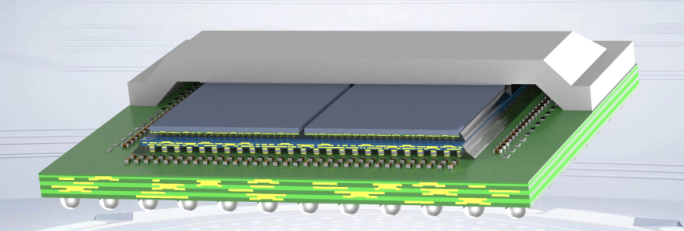

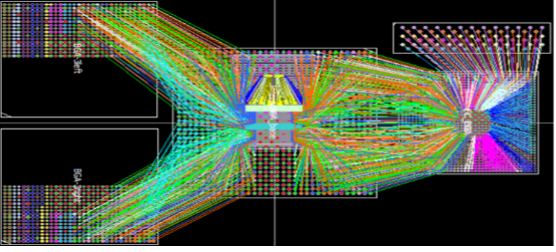

第三种技术方案,FOCT-R- Heterogeneous Chips High Density Fanout Integration/异质芯片超高密度扇出型互联技术,该技术典型的应用为GPU/CPU等核心数字芯片和HBM-High Brand Memory 芯片的互联技术,该技术芯德科技全面开始联合国内领先的GPU厂商开始Test Chip 的设计与开发,计划采用的结构为:1 core GPU Chip to connect with 4HBM Chip, 其中关键的Interposer 的设计规范已经打通,有机会成为国内首家完成真正的异质结构互联封装技术的高端封装公司。

图8 Core Concept: Heterogeneous Chips High Density Fanout Integration/异质芯片超高密度扇出型互联

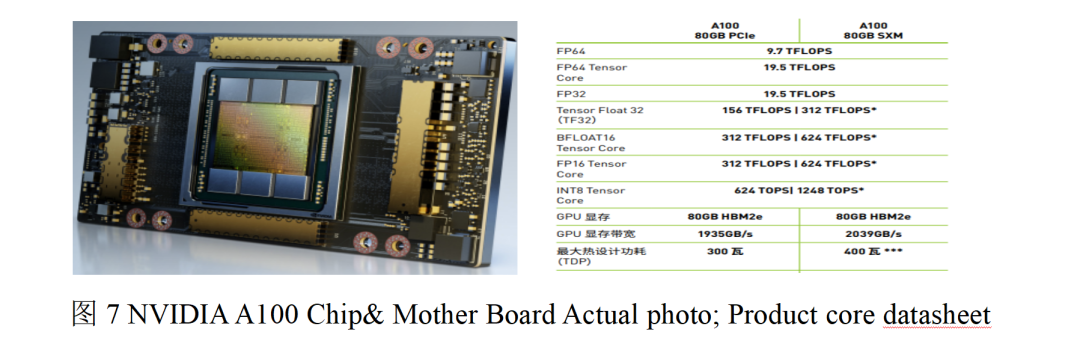

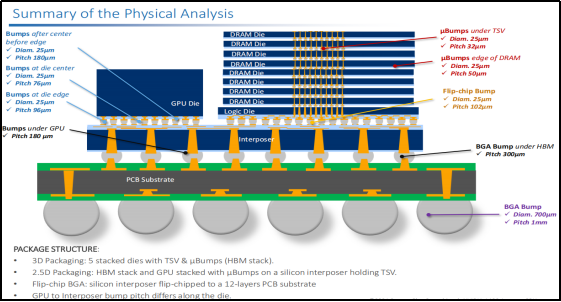

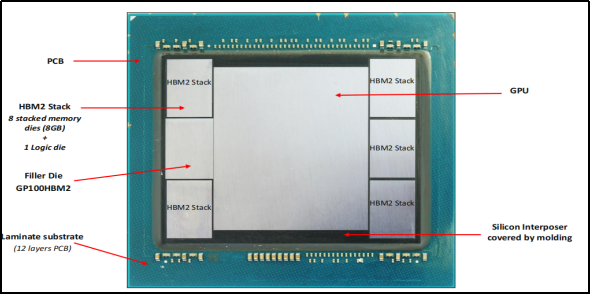

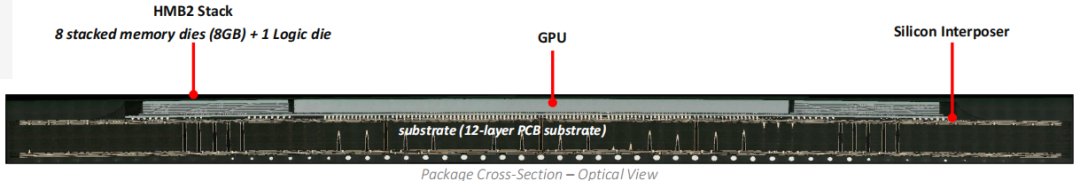

因异质高密度扇出集成封装集成对于设计公司要求较高,需要从Chip architecture即芯片系统架构上布局软件和硬件上打通核心计算芯片与HBM的互联,目前使用改设计技术的公司尚集中在非常有限的几个公司,作者有幸有机会参与了NVIDIA A100 Ampere 40GB HBM2芯片的解析,在此也分享给集成电路产业界的朋友,该资料出于非商业化的解密分享阶段。NVIDIA A100 Core GPU 可针对 AI、数据分析和 HPC 应用场景,在不同规模下实现出色的加速,有效助力更高性能的弹性数据中心。A100 采用 NVIDIA Ampere 架构,是 NVIDIA 数据中心平台的引擎。A100 的性能比上一代产品提升高达 20 倍,并可划分为七个 GPU 实例,以根据变化的需求进行动态调整。A100 提供 40GB 和 80GB 显存两种版本,A100 80GB 将 GPU 显存增加了一倍,并提供超快速的显存带宽(每秒超过 2 万亿字节 [TB/s]),可处理超大型模型和数据集。产品功耗控制在300~400W能力。

A100芯片BGA final PKG size 在55X55mm, Interposer的设计尺寸在43X37mm, 在Interposer 上集成了7颗芯片;中间最大一颗是TSMC- 12inch/FINFET/18 metal layers/7nm 工艺, 芯片尺寸Die area: 826.88 mm² , (32.3 x 25.6 mm),64 chips per wafer;其余的5颗是HBM Chip,另外一颗是Dummy Chip 用来平衡系统的热应力等因素。

整个A100的核心链条包括TSMC-FAB,Samsung-HBM Stack, IBIDEN ABF substrate, 以及TSMC-2.5D PKG 解决方案,从芯片7nm制程到基板的制造,都是业界非常值得学习和研究的一颗核心芯片。

A100 芯片采用的是COWOS-S的制程技术,代表了在拥有了FABTS核心工艺的情况下,业内目前量产较多的技术应用,但现阶段该技术因为成本、良率、交期、产能等诸多原因,目前只有国际上为数不多的厂商在使用该技术做产业化的推进;作者曾经和国内某一线GPU厂商进行过技术分析以及供应链商讨,COWOS-S的封装交期在3个月以上,给设计公司在整个项目推进上带来了较多的挑战;正如大家所知,TSMC近来推出来的COWOS-R即通过制作RDL有机载板的技术路线也是一种尝试。

芯德科技FOCT-R互联技术旨在帮助客户提供一种新的解决方案,从而实现超高密度的芯片互联技术;当然FOCT-R 和 CoWoS-S 相比,CoWoS-S 有他的技术优势,因为COWOS-S的Silicon Interposer 是在Wafer FAB 制程中完成,所以有些被动元器件IPD-Integrated Passive Device 集成在Interposer里面,这样就不用在基板上再进行被动元器件的贴装。目前我们正和客户设计团队对齐FOCT-R的技术方案,我们采用的是在BGA基板上进行诸如电容器件的贴装等工作。 产业链上来看,关于高密度扇出型封装技术发展方面,在中国大陆的封测企业中,目前仅有为数不多的公司具备相关技术开发能力。2021年,长电科技推出了XDFOI全系列极高密度扇出型封装解决方案。通富微电在Fanout、2.5D、3D堆叠等方面均有布局和储备,并且在产业化方面在做全方面的推进。 芯德科技全方面的CAPiC技术平台解决方案为客户带来更多的选择,已经有多个国内外客户导入FOCT-R的技术,目前处于产品设计阶段,产业化的趋势和机会值得期待。其他的技术平台比如eWLB-F& eWLB-M 等都已经实现了产业化的推进,TGV的技术开发已经和业界专家行了战略合作关系,全面推进在射频应用领域的合作与推进。 客户端的解决方案方面,芯德科技的FOCT-R技术业界推广已经取得了很大的突破,对于同质结构的互联技术,芯德已经和3家客户开始实际项目的推进,其中采用TSMC-5nm 双芯片同质互联的项目即将在2023/5 开始正式启动;异质互联方面,芯德科技和一线GPU厂商在展开同步的设计工作,计划采用1GPU+4HBM的方案来进行NPI的设计以及产业化推进工作。

原文始发于微信公众号(芯德科技):芯德科技FOCT 高性能芯片互连技术给客户带来更多选择