来源:内容由半导体行业观察(ID:icbank)编译自semianalysis,谢谢。

在之前的报道《先进封装最强科普》和《巨头们的先进封装技术解读》中,我们对高级封装的必要性和基本概述以及重点逻辑产品提供的主要类型、内存和图像传感器封装模式进行了介绍。在本文里,我们将讨论热压粘合 (thermocompression bonding:TCB) 以及该领域的 3 家主要工具厂商 ASM Pacific、Kulicke 和 Soffa 以及 Besi。热压键合是标准倒装芯片工艺的演变,但涉及许多优点和缺点,我们也将在此讨论。

热压键合 (TCB) 用于所有当前形式的 HBM 存储器。英特尔的大部分封装技术也使用 TCB。英特尔对该技术压下了非常大的赌注,将其作为其封装需求的驱动力,而台积电根本没有效仿。我们将讨论这项技术如何以及英特尔在其开发中的独特作用,这使他们能够成为先进封装的领导者,但我们还将讨论一些缺点。英特尔希望继续在 TCB 工具上花费数亿美元的订单,用于在亚利桑那州、新墨西哥州的扩张以及在马来西亚新建的 70亿美元封装设施中。我们将首先解释该技术、英特尔在该技术开发中的主要作用,最后是工具生态系统。

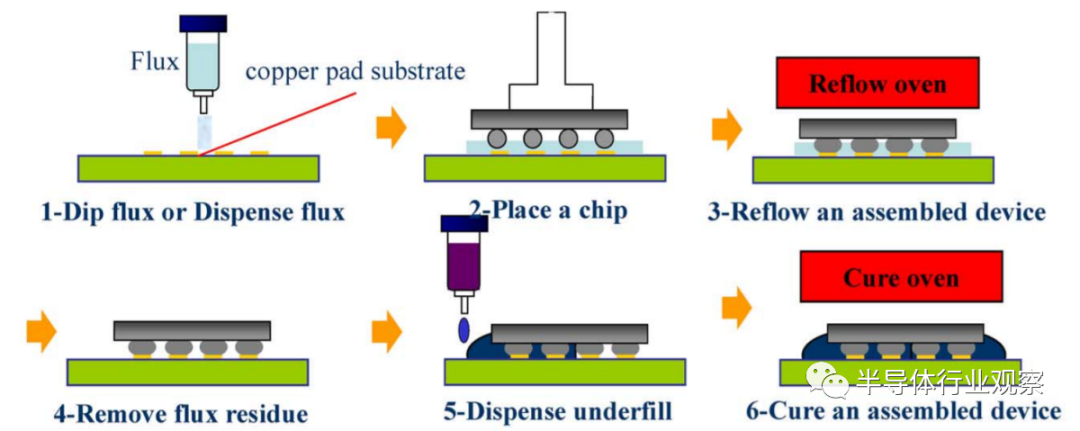

要了解TCB的优势,首先要说一下倒装芯片封装的弊端。如在《巨头们的先进封装技术解读》中所述,标准倒装芯片工艺从沉积助焊剂或非导电浆料开始。然后,芯片放置工具将芯片准确地放置在基板、中介层或载体上。这是在批处理过程中完成的,因此许多封装可以一次放置它们的裸片。然后将放置的模具组进入回流炉,这也是一个批处理过程。将数十个、数百个甚至数千个封装放入烤箱中,加热到使焊料熔化的温度以完成粘合,然后继续进行后续步骤,例如去除助焊剂残留物和底部填充。

这个过程非常快,但也有一些主要缺点。最大的问题与热膨胀系数 (coefficient of thermal expansion:CTE) 有关。因为整个封装由许多不同的材料组成,在回流炉中加热会导致这些不同的材料以不同的速率膨胀。下面我们将举个例子,虽然这不是最好的类比,但还是有参考意义。如果你曾经烤过馅饼,你就会知道馅饼皮,馅饼的馅料不会以同样的速度膨胀。如果您对几个不同的因素不小心,您的馅料最终会在外壳的顶层沸腾并使外壳湿透。

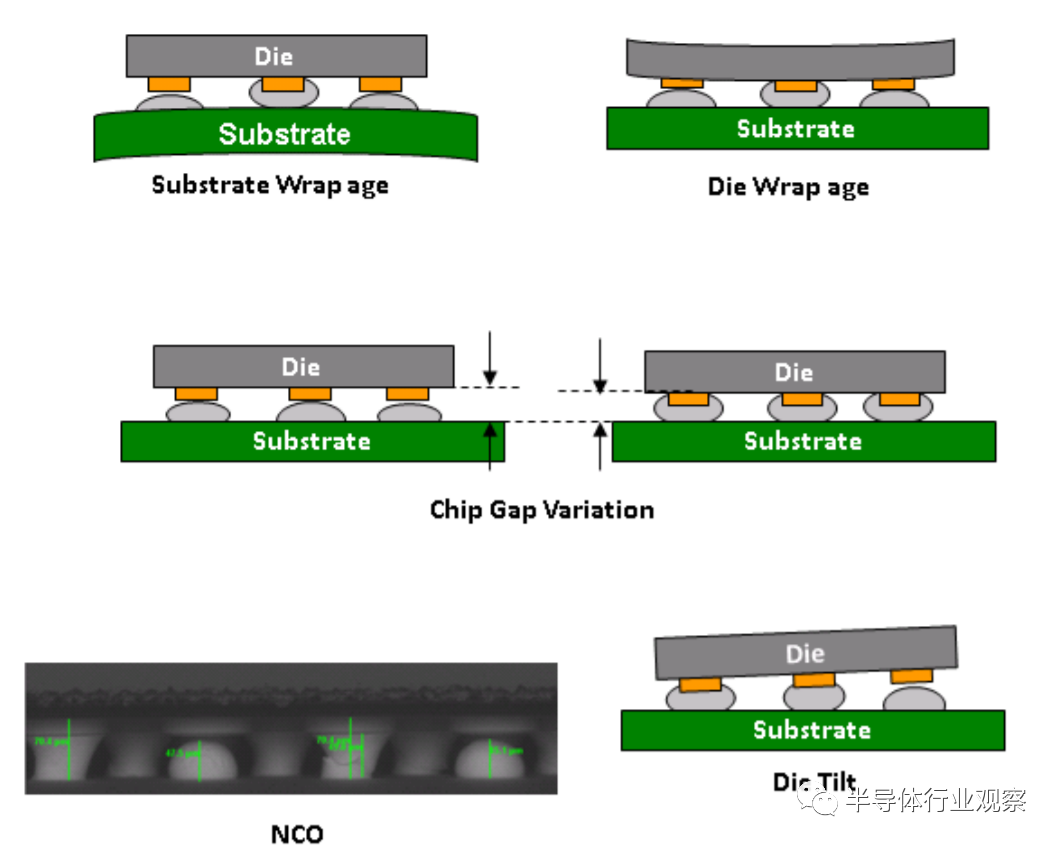

随着芯片和基板膨胀和冷却,CTE 的差异会导致翘曲。此外,由于芯片是放置后重新焊接的,焊球可能无法与每个铜焊盘完美接触,从而导致芯片间隙变化。最后,Die可能无法完全平整放置。随着时间的推移,这些小问题会累积起来,导致早期故障或更差的电气性能。

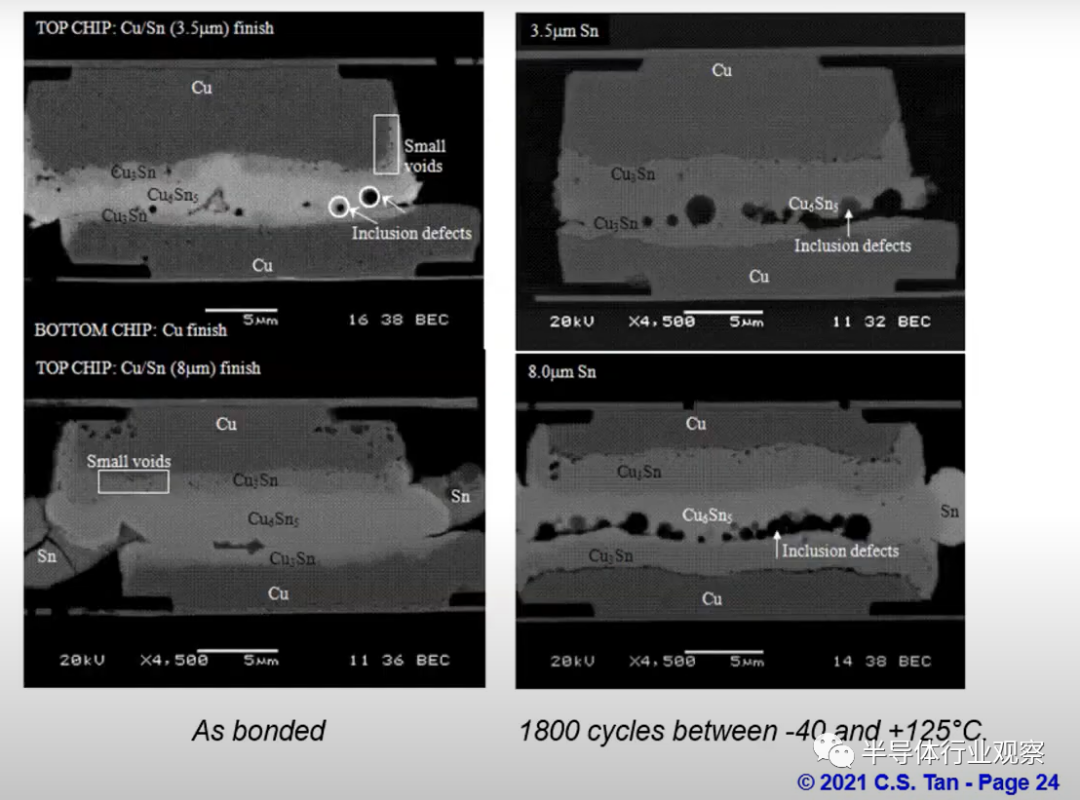

业界只能关注许多原始的无源中介层技术。AMD 基于Fiji的 GPU 的故障率非常高,因为该过程没有产生完美的粘合,最终热循环导致产品无法正常工作。随着 TSMC 和 ASE/SPIL 学会了如何进行基于中介层的封装,这些可靠性问题随着时间的推移而有所改善,但尚未完全解决。在温度不稳定且封装频繁在高温和低温之间循环的环境中,这些问题仍然比较常见。

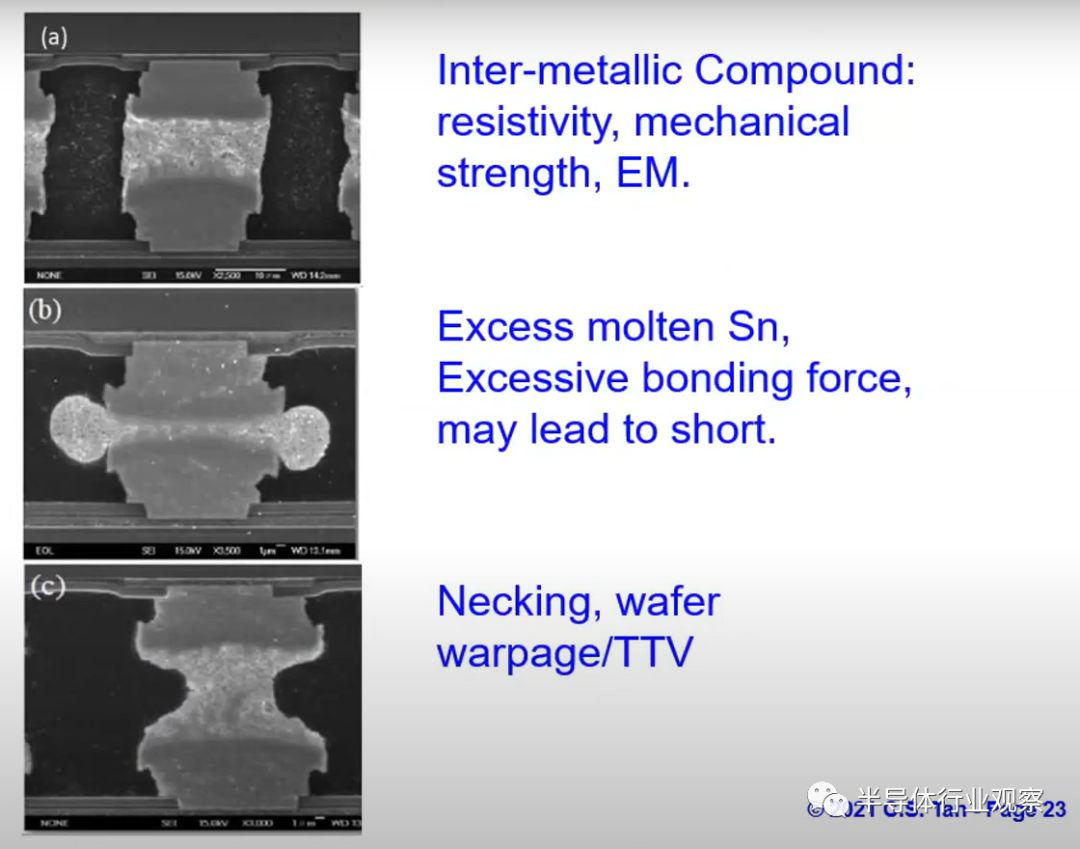

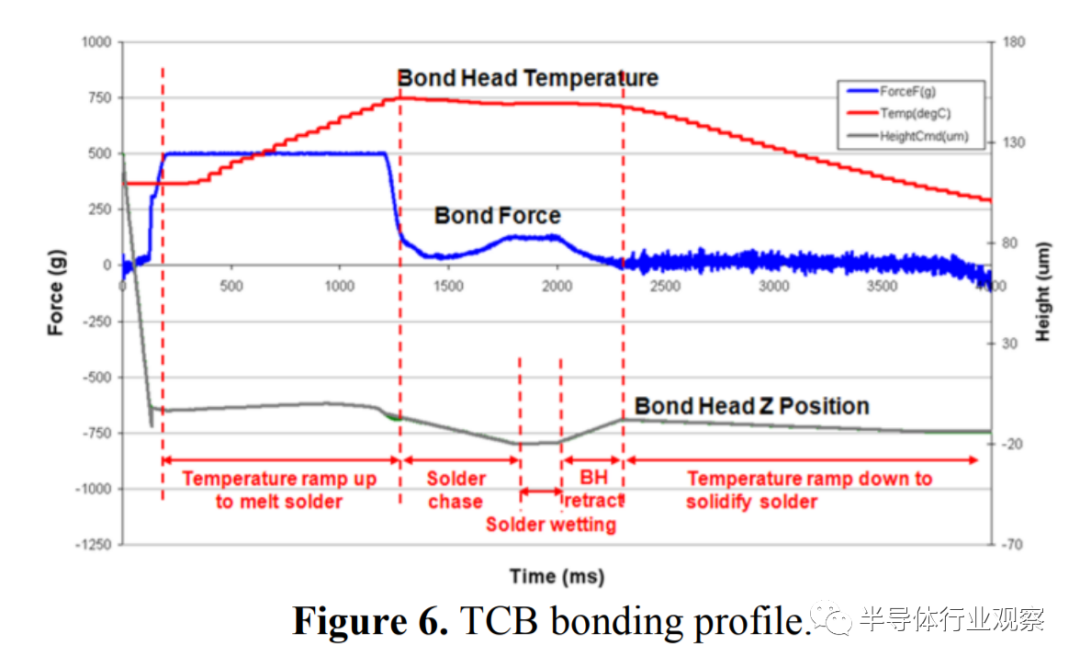

来到热压粘合。虽然我们无需在批处理过程中放置芯片并将整个组件运送到回流炉,而是使用单一工具放置单个芯片,施加压力并加热它们以回流焊球。这种方式解决了标准倒装芯片的几个主要问题。从芯片顶部加热,因此只有芯片和 C4 焊接连接会发热。这避免了基板翘曲问题。该力确保均匀粘合,没有间隙变化或倾斜。最后,当施加该力时,会伴随着快速振动,从而破坏铜焊盘和焊球上的金属氧化。几乎没有空隙和污染的粘合。

TCB 在相同的 IO 间距下实现更好的电气特性。TCB 允许 IO 间距缩放到更小的尺寸。TCB 还可以封装更薄的芯片和封装。后者是 HBM 使用 TCB 的原因,也是华为在移动芯片市场上尝试使用 TCB 的原因。与标准倒装芯片工艺流程相比,TCB 似乎是一种完全更好的技术,但这忽略了一个主要因素。

再看成本,一个先进的 TCB 工具每小时可放置 500 到 1,000 个Die,成本约为 125 万美元。另一方面,先进的倒装芯片芯片放置工具每小时可放置 3,000 到 10,000 个芯片,成本约为 450k。这些数字差异很大,具体取决于精度与吞吐量的权衡以及工具可能附带的各种功能,但其明显的标准倒装芯片的吞吐量要高得多。回流炉非常便宜,可以处理许多贴片工具的输出,因此成本不值得担心。

令人好奇的是,英特尔拥有近 300 种 TCB 工具,而在马来西亚的封装工厂,这些工具的数量翻倍。这 300 种工具远远超过了英特尔的先进封装用途。英特尔在许多非高级封装应用中使用 TCB,在这些应用中,标准的倒装芯片工艺非常适合。

SemiAnalysis 私下与一位英特尔封装工程师进行了交谈,理由很有趣。鉴于英特尔在高功率和高利润应用中占有很大份额,产量损失和可靠性问题远远超过了每单位封装工具的微不足道的摊销成本。

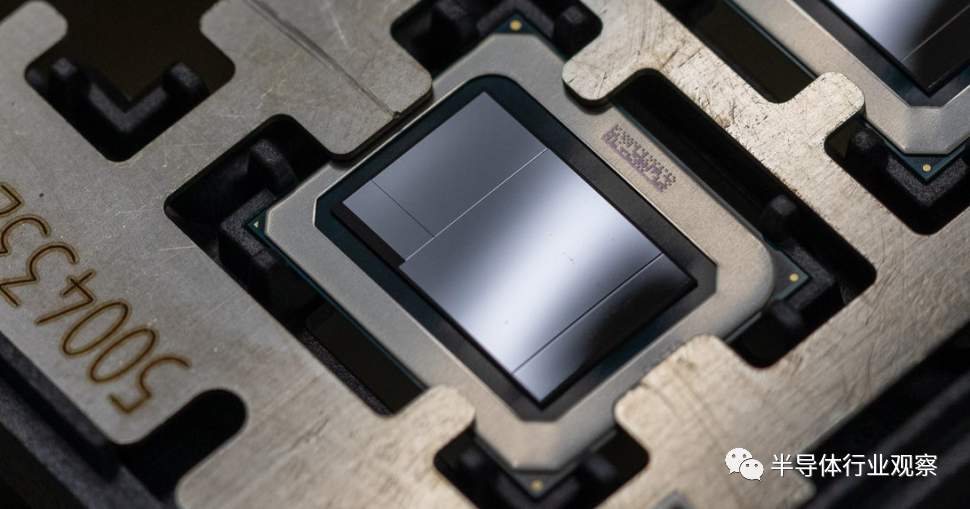

此外,这些工具在封装类型方面提供了很大的灵活性。英特尔可以对标准封装、2.5d 封装和高级 3d 封装使用相同的工具。上图来自der8auer,它展示了具有多种间距尺寸的 Intel Sapphire Rapids 服务器 CPU。EMIB 的间距为 55 微米,其余的Die与封装连接的间距为 100 微米。虽然理论上这在没有 TCB 的情况下是可能的,但考虑到焊盘和焊帽尺寸的差异,在现实世界中的实施要容易得多。

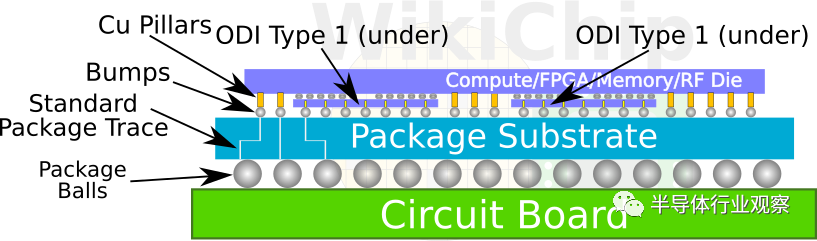

当英特尔转向 Foveros Omni 时,TCB 的功能真正开始大放异彩。我们在上述文章中讨论了该技术,但铜柱和 ODI 裸片使 Foveros Omni 几乎无法使用标准倒装芯片工艺进行封装。第一款 Foveros Omni 产品将是英特尔的 Meteor Lake,这是一种大众市场客户端架构,专为 5W SOC 一直到高功率台式机而设计。尽管包含许多裸片,Omni 仍可大幅节省制造成本,为 IP 选择最佳工艺节点并最小化裸片尺寸以提高产量。该封装具有 130 微米、100 微米和 36 微米的各种凸块间距。高级 3D 逻辑封装不仅适用于高性能应用。

台积电、三星和许多其他公司将无法进行这种封装,除非他们在 TCB 上投入巨资。十多年来,英特尔一直在共同开发 TCB 工具,因此竞争对手很难立即转向这项技术。台积电的 InFO 采用标准倒装芯片流程,同时由于基板更昂贵,可能是一种更昂贵的封装技术。台积电没有先进的封装,而是在商品标准的 ABF 基板上,这阻碍了他们在成本方面能够将先进封装降低多远。同时,InFO 确实具有我们在第 2 部分中讨论的一些主要优势,即与 RDL 内的复杂布线相关,无需使用硅片。

混合键合的功能超出了倒装芯片 TCB 所能提供的任何功能,但该技术在成本和性能曲线上的运行点完全不同,这削弱了其在中期内增加产量的能力。这将在未来讨论。

英特尔对 TCB 的支持使他们能够围绕各种 IP 创建可选性,并在许多不同的节点上制造许多不同的块,而不会对 die-to-die 连接造成很大的损失。设计方面的策略细节在这篇关于英特尔台积电晶圆供应协议的文章中进行了讨论。

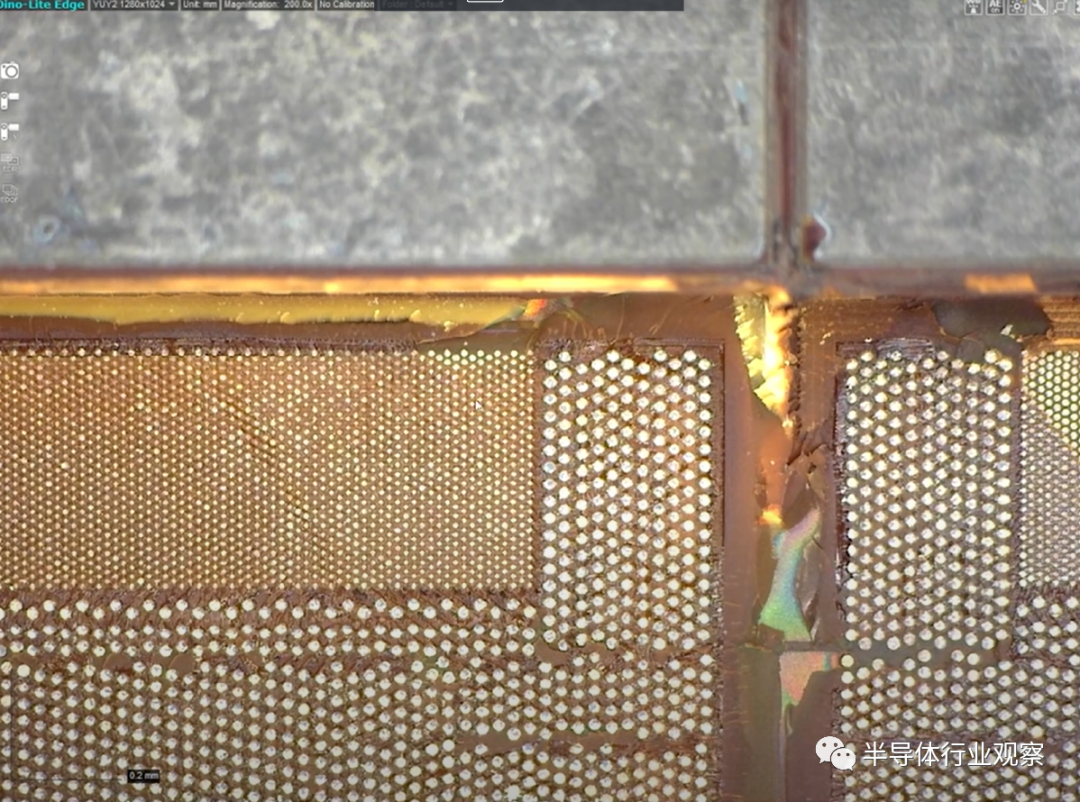

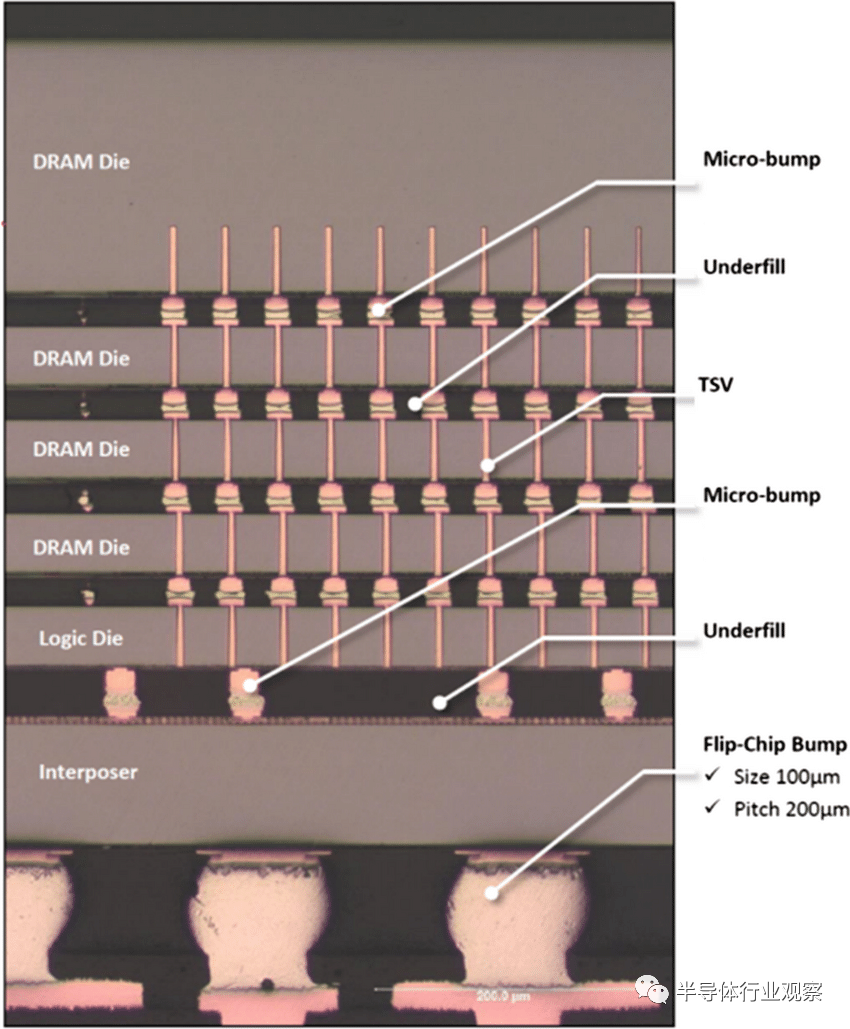

TCB 也已在 HBM 应用中采用。HBM die需要非常薄。上图只有 4 个堆栈,但随着行业扩展到 8 个堆栈甚至更多,三星、SKHynix 和美光必须使用 TCB。在 SKHynix 即将推出的 12 堆栈 HBM3 中,对裸片薄度的要求变得如此极端,每个裸片都被减薄到 30 微米。凹凸间距同样非常密集。目前启用 HBM 堆栈的唯一方法是使用 TCB 技术,但业界期待可能使用更奇特的封装形式,例如混合键合。

由于 TCB 是封装极薄芯片的最佳技术,因此 TCB 还通过使用 OSAT 和 IDM 封装的旗舰设备中的手机应用进行了试验。三星、高通/Amkor 和华为/ASE 在一些与封装上封装 (PoP) DRAM 相关的应用中使用了 TCB。OSAT 开始订购越来越多的 TCB 工具,但最大的订单仍然来自英特尔及其定制的共同开发的 TCB 平台。关于这些其他用例需要注意的重要一点是,它们与英特尔的工具不同,它们也不是为高功率或高性能应用而设计的。

ASM Pacific、Kulicke 和 Soffa 以及 Besi 之间的市场对 TCB 来说是非常活跃的,并且每家都在不同的领域表现出色。这导致每个人都有自己的利基市场。订单簿正在大幅上升,但由于它们各自占据的利基市场,这三个方面并不一致。

原文始发于微信公众号(半导体行业观察):先进封装,英特尔在这个环节领先台积电