随着AI算力芯片向大尺寸、高集成度演进,传统封装基板逐渐逼近物理极限。玻璃基板凭借更低信号损耗、更高尺寸稳定性等优势,成为台积电、英特尔等巨头布局CoWoS、HBM等先进封装技术的优选载体。

8月27日—深圳,第二届玻璃基板TGV及板级封装产业高峰论坛和2025年玻璃基板及封装产业链展览会精彩持续,今日论坛的会议主题是板级封装,下面与大家一起回顾下演讲内容。

一、演讲嘉宾

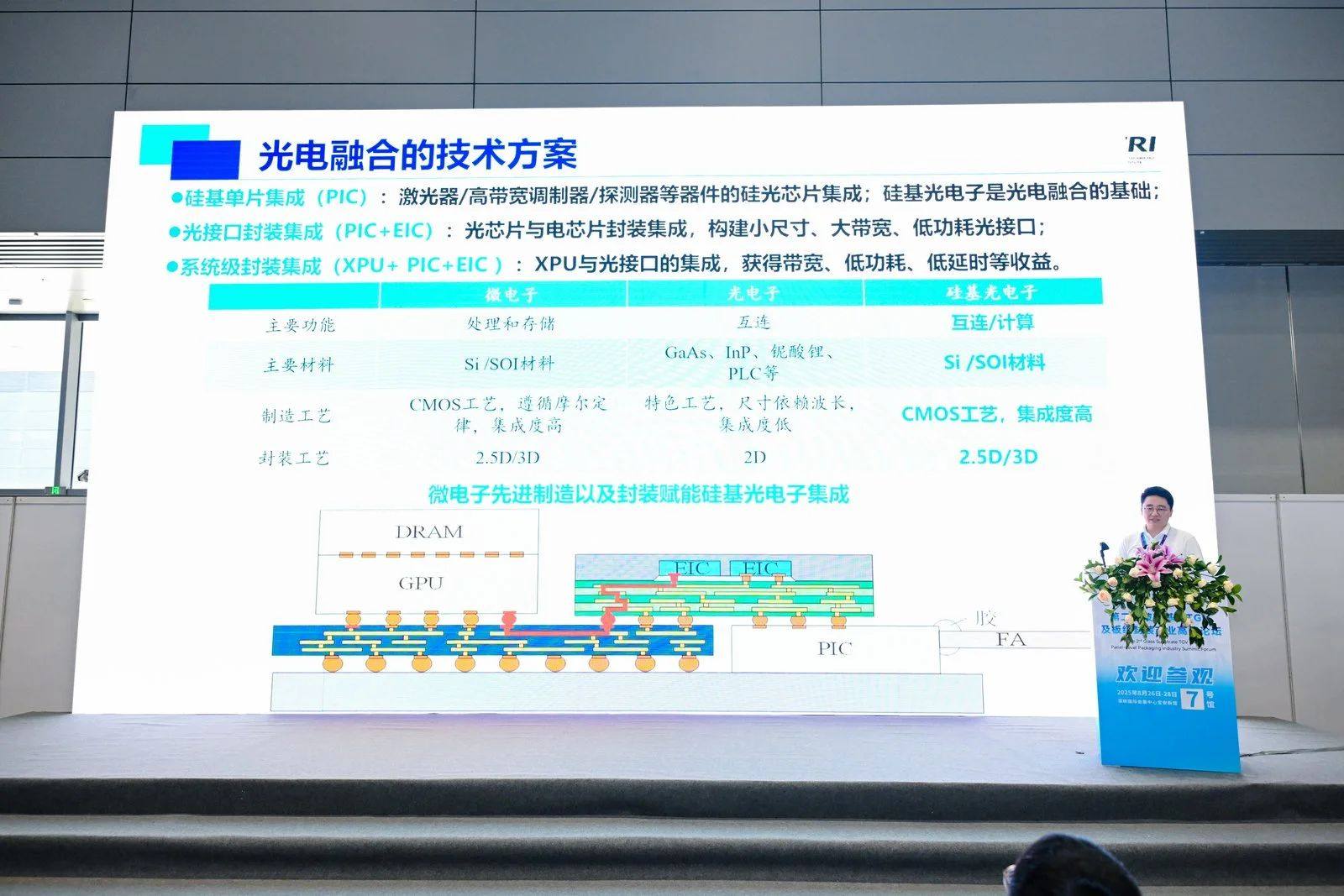

1、《面向大算力应用的硅基光电融合先进封装技术》

华进半导体封装先导技术研发中心有限公司 主任研发工程师 严阳阳

随着人工智能、高性能计算和高速光通信的飞速发展,我们正站在一个技术变革的临界点上。传统的电子互联已逐渐面临带宽和功耗的瓶颈,而光电融合,这项被视为“后摩尔时代”破局的关键技术,正为我们开启一扇通往更高算力、更高能效未来的大门。

本次论坛华进半导体主任研发工程师严阳阳主要从光电融合的封装技术、非硅器件集成以及光电共封演进、光电融合技术战略意义和国内外光电融合生态对比等方面介绍了《面向大算力应用的硅基光电融合先进封装技术》报告。光I/O以及CPO是芯片技术,也是系统技术,是AI算力未来核心技术,直接和国家经济和国防命脉紧密连接在一起,中国非常需要一流的光电融合企业。光电融合技术通过先进硅光芯片、集成电路和光电共封等有机融合,以实现芯片间光电互连技术全链条创新,它追求芯片和系统上的颠覆性创新。

最后还介绍了华进半导体是国家集成电器特色工艺及封装测试创新中心,与多家头部企业和研究院所合作研发3D光学引|擎封装技术。华进拥有一条8/12吋兼容的晶圆级先进封装中试线和配套封装产线,其中TSV Interposer、Fanout和FCBGA等成熟产品的产能分别为1000片/月、1000片/月和100万颗/月。

2、《应用于三维封装的PVD 系统》

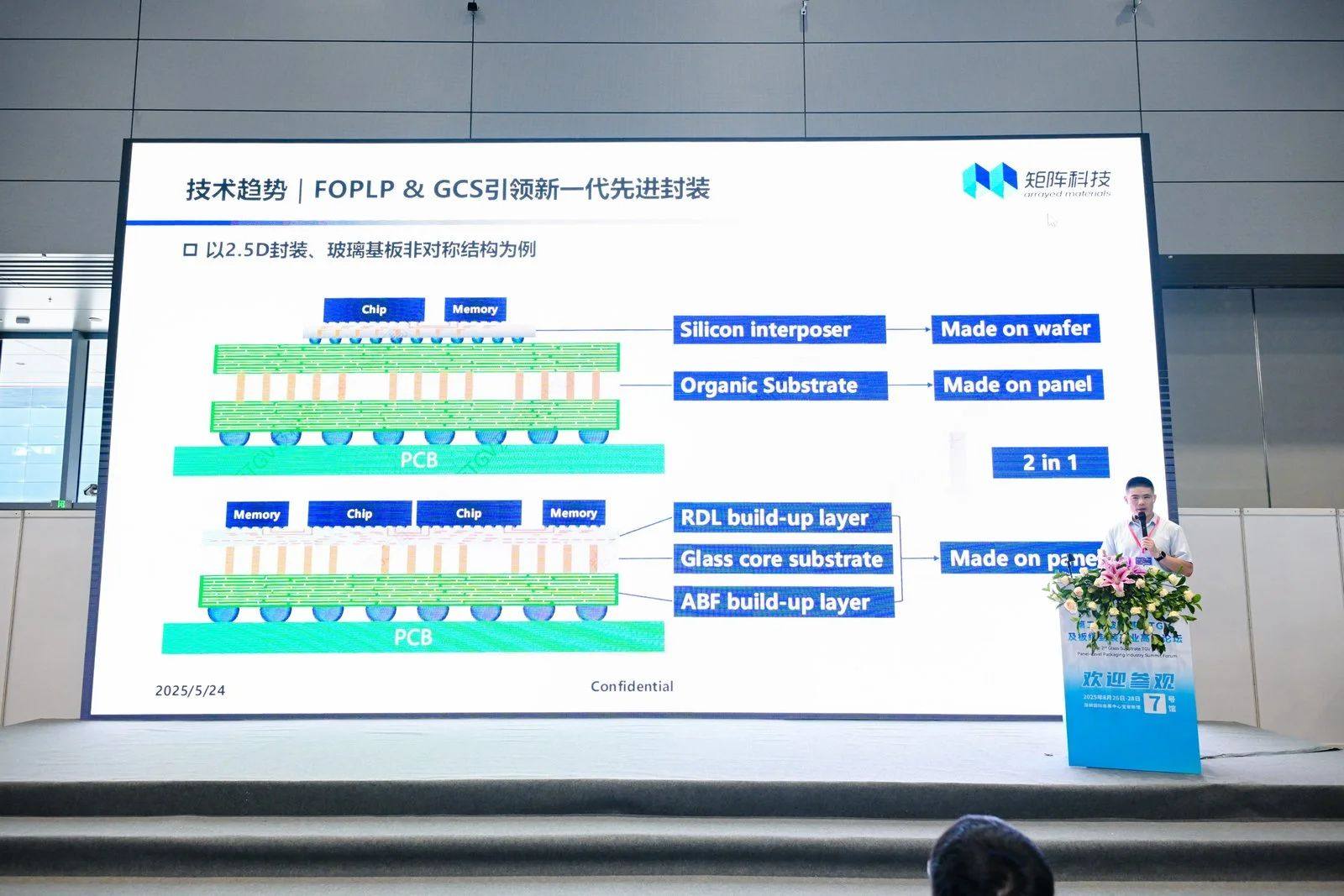

深圳市矩阵多元科技有限公司 董事长 张晓军

先进封装,尤其是三维(3D)封装技术,薄膜沉积(PVD) 作为其核心工艺环节,直接关系到互连的可靠性、性能的优劣以及最终的成本控制。可以说,PVD技术的每一次革新,都在为芯片性能的飞跃和形态的革新注入强劲动力。

在本次论坛上矩阵多元科技董事长张晓军主要从技术趋势、玻璃基板、设备优势、从CoWoS到CoPoS、TGV工艺流程及典型设备供应商等方面给大家详述了《应用于三维封装的PVD 系统》。

张晓军董事长指出:FOPLP & GCS引领新一代先进封装;玻璃基板,因其优异的物理特性,在高性能和高密度封装中展现出较大潜力;专门针对TGV进行优化设计的PVD是实现高深宽比玻璃基板大规模量产的最佳选择。

最后张晓军董事长详述了公司设备的优势以及公司的简介,张晓军董事长介绍到自己开发了英特尔、台积电和三星等主流 半导体制造公司生产线广泛应用的 PECVD系统,发表了20余篇SCI论文且拥有超200 项专利。目前公司面板级先进封装 PVD 量产设备已经发往客户。

3、《化圆为方:面板级封(PLP)实现异构集成芯未来》

亚智系统科技(苏州)有限公司 Manz亚智科技事业开发部副总经理 简伟铨 Adam

当我们将这些精密的芯片和互连结构,从传统的圆形晶圆迁移到更大的方形面板上进行集成时,不仅是生产载板形状的改变,更是一场旨在突破摩尔定律极限、追求极致效率与成本的“封装革命”。

在本次论坛上亚智科技开发部副总经理简伟铨主要从公司介绍、解决方案、先进封装市场趋势、面板级封装市场预测、RDL 制程设备、TGV电镀设备等方面给大家详述了《化圆为方:面板级封(PLP)实现异构集成芯未来》。

简伟铨副总经理介绍到:台积电、三星及英特尔发展芯片制程微缩至3nm节点,持续朝2nm以下技术迈进,在面临挑战物理极限的情况下,技术开发难度及成本都将大幅上升。为持续增加单位面积的晶体管数量,各厂商积极发展不同先进封装技术,透过立体堆栈结构与异质整合跨越摩尔定律。

2.5D / 3D先进IC封装技术(e.g. CoWoS) 2023 ~ 2029年的年复合年增长率为 18%,至2029年将占近40%市场。已经成为代工厂、封测厂、IDM、芯片设计厂商以及EDA厂商都竞相关注的一环。

亚智科技可根据客户不同的导电层架构和封装技术,提供相应的RDL制程设备解决方案;跨领域客户快速整合制程技术及设备,缩短产品开发周期;提供完整的RDL解决方案,快速进入量产阶段。

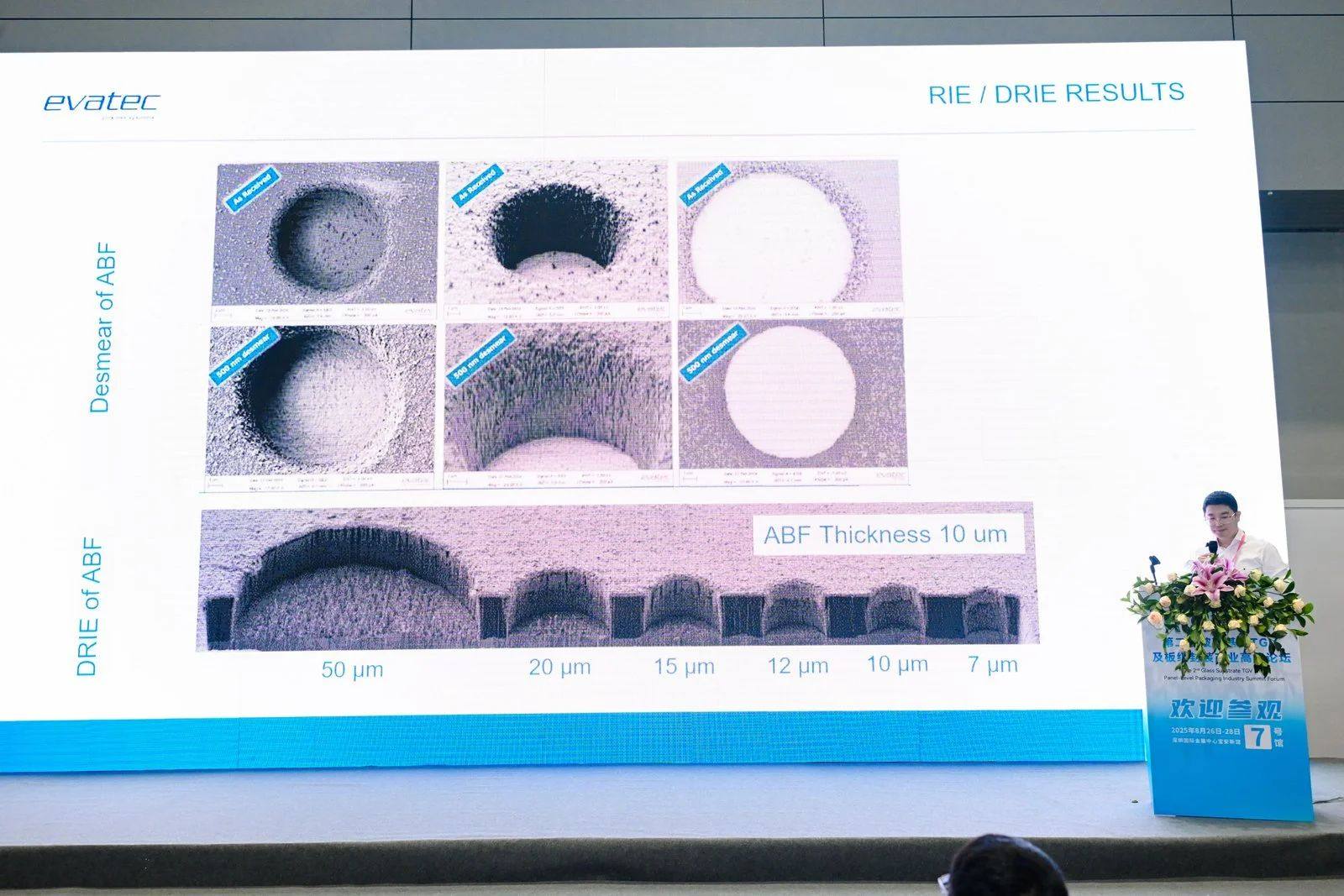

4、《Evatec先进封装基板FOPLP刻蚀和溅射方案》

Evatec China 技术市场总监 陆原博士

任何宏伟蓝图和尖端架构的实现,都离不开最底层、最精密的制造工艺与装备的支撑。尤其在面板级封装这片新兴的沃土上,刻蚀与溅射(PVD) 这类关键的薄膜工艺,直接决定了线路的精度、互联的可靠性以及最终产品的性能与良率。

在本次论坛上,陆原博士主要从公司介绍、先进封装设备、等方面给大家详述了《Evatec先进封装基板FOPLP刻蚀和溅射方案》。

公司的CLN300和600设备主要应用在先进封装板块,在先进封装领域攻克了一系列技术难点。CLN600目前在全球装机量比较多,设备靶材利用率较高,目前差不多有15台装机量,全球市场占有率58%。

关于最新机型,公司推出了应用于310x310mm基板的设备,相比之前设备在ETCH和PVD部分进行了调整。

最后总结到,公司主要基于经过验证的CLN300技术新开发,提供RDL和BSM解决方案,已从国际客户处获得订单。

5、《蓝宝石晶圆在先进封装与功率半导体领域的发展与挑战》

天通银厦新材料有限公司 副总经理 康森

天通银厦副总经理康森《蓝宝石晶圆在先进封装与功率半导体领域的发展与挑战》报告阐述了蓝宝石晶体材料的特性,以及在功率半导体(作为GaN外延衬底)和先进封装(临时键合载板/基板)领域展现出独特的应用价值与潜力。

蓝宝石在功率半导体中作为衬底,具有高绝缘性、晶格匹配和热化学稳定性等特点。氮化镓功率芯片通过将氮化镓薄膜沉积在硅基衬底或蓝宝石等其他合适的衬底上,形成氮化镓晶体,从而实现功率芯片的制造。蓝宝石在先进封装中作为载盘,拥有独特且不可替代的优势组合(高导热+高稳定性+高透明度+低CTE等),尤其在需要光学互连或极端要求平整度、稳定性、散热和可靠性的特定高端应用中,存在明确的机会。在扇出型(FanOut)和三维(3D)等先进封装工艺中,蓝宝石凭借其高硬度和抗高温翘曲能力,耐高温循环,易于移除且不损伤基板等性能,成为理想的临时载盘材料。

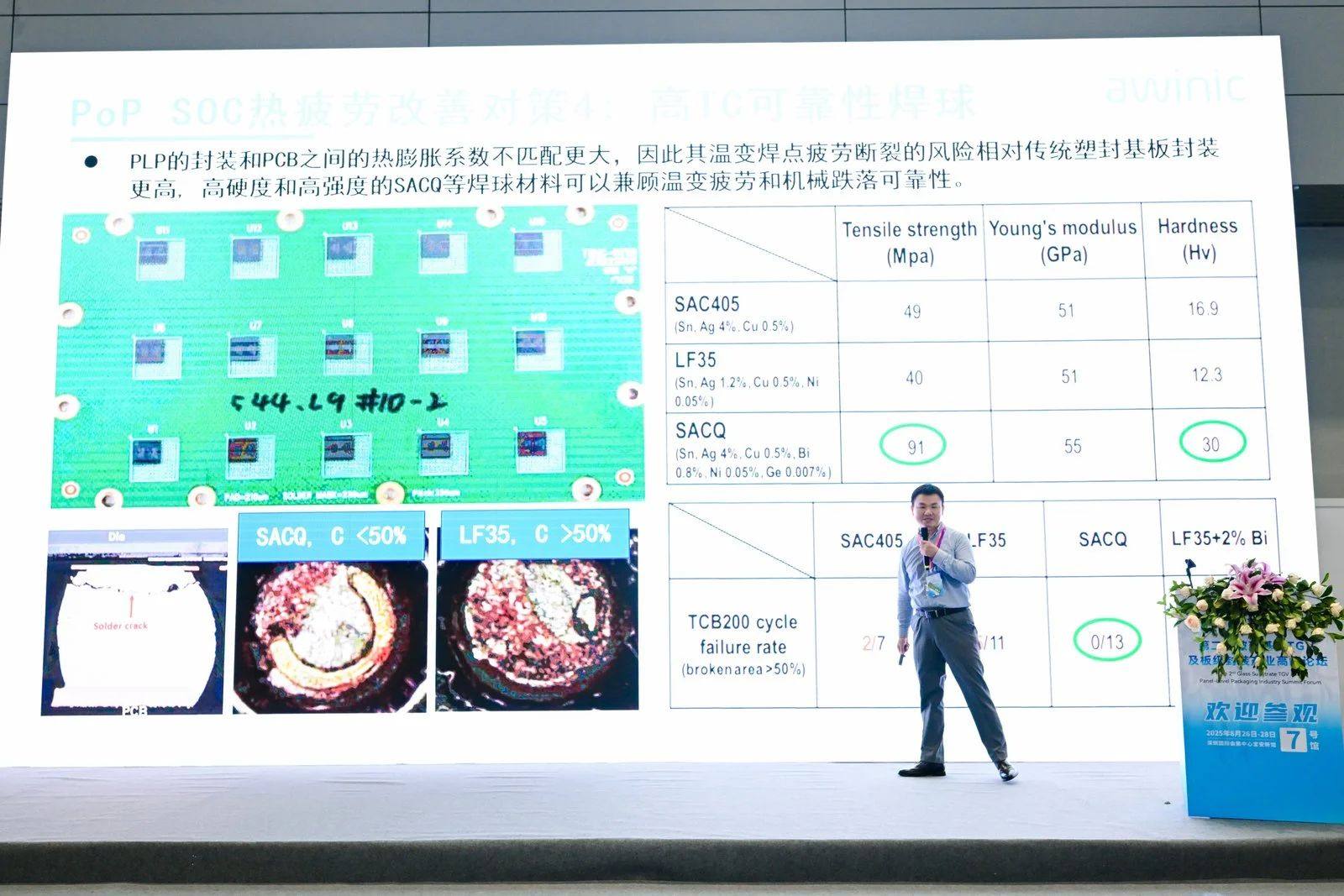

6、《FOPLP应用工艺可靠性挑战及封装板级协同设计解决方案》

上海艾为电子技术股份有限公司 芯片封装首席专家 史洪宾 博士

艾为电子芯片封装首席专家史洪宾博士在《FOPLP应用工艺可靠性挑战及封装板级协同设计解决方案》报告中系统阐述了FOPLP 封装的技术现状、挑战和解决方案。

面板级封装主要技术包括FOWLP面板、玻璃中介层板、有机中介层、混合中介层板、嵌入式芯片。PLP相对WLP更高的载体面积使用率& 更大的载体面积,有助于提高封装生产效率和降低成本,使得PLP在从消费类型电子到AI都将得到广泛应用。报告还介绍了FOPLP 等封装板级焊点可靠性挑战是国产化,消费类电子FOPLP的发展趋势 & 热应用环境变化、热疲劳断裂失效机理,以及改善热疲劳的对策。重点介绍了FOPLP RDL / FOPLP Via 的可靠性挑战和可靠性设计。随着PLP持续向细间距演进,以及与WLP差异化的介电等材料体系,都让RDL的可靠性风险需要被特别关注。

7、《高精度非接触测量机在玻璃基板以及ABF载板行业中的应用》

Mitutoyo/三丰精密量仪(上海)有限公司 营业技术部部长 李斌

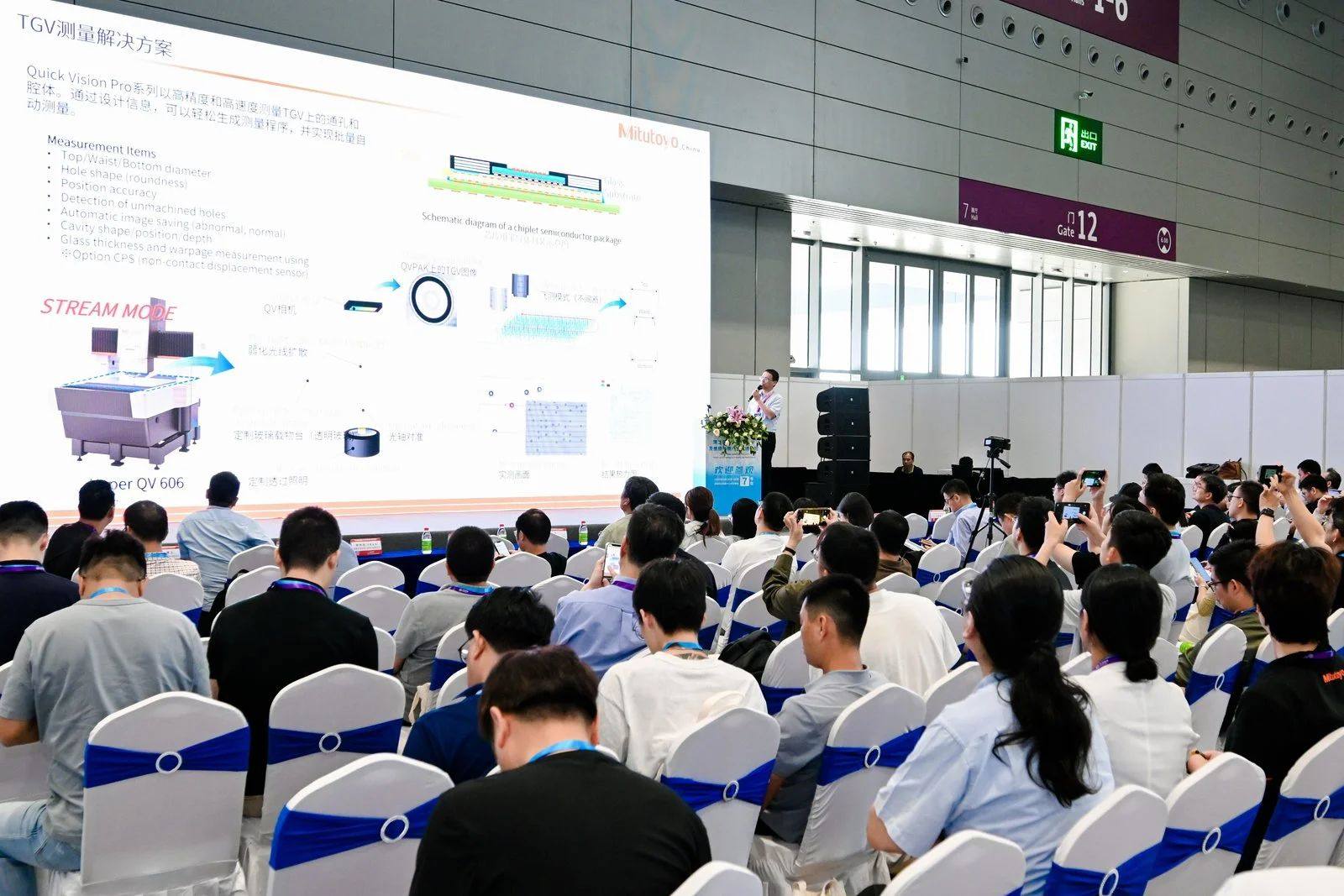

本次论坛Mitutoyo/三丰精密量仪(上海)有限公司营业技术部部长李斌主要从载板行业发展和检测需求、主流测量方案比较和测量难点、玻璃基板测量方案及应用案例、ABF基板和板级封装测量方案及应用案例四个方面分享《高精度非接触测量机在玻璃基板以及ABF载板行业中的应用》报告。

TGV检测需求方面,通常包含玻璃基板、通孔加工、种子层沉积、电镀铜、RDL、Bump、芯片贴装和可靠性测试,三丰主要集中在通孔加工等方面。三丰还介绍了公司的TGV测量方案,Quick Vsion Pro系列以高精度和高速度测量TGV上的通孔和腔体。通过设计信息,可以轻松生成测量程序,并实现批量自动测量。例如,HYPER QV606机型主要功能包含:1)国定桥式·ISO标准·实时温度补偿;2)Stream (飞测);3)TAF(走动跟踪对焦);4)彩色LED照明·图案对焦。

面板级封装中的贴装精度方面,面板级封装中Die或Chiplet的贴装精度至关重要,会直接影响到后续的光刻制程。Quick Vsion Pro系列可快速测量芯片贴装和RDL固化制程后的芯片位置、角度偏移等尺寸,帮助修正制程能力,还可输出RDL的坐标补偿数据,提供给后续制程做对位使用,以满足量产需求。

其中FOPLP的封装方法与F0WLP类似,采用更大的矩形面板上,解决了晶圆封装会导致边角面积浪费的问题,有更高的封装效率。HYPER QV606有效测量行程600x650mm,可对应515mmx510mm和600mmx600mm尺寸的面板。可配置防静电多区陶瓷真空吸附台来固定面板,防止翘曲。可按要求制作中空结构,防划伤。

8、《涂布、干燥、贴膜工艺设备于玻璃基板及扇出型封装的应用趋势与挑战》

群翊工業 副總经理 李志宏

先进封装技术的实现,是一座由精密材料、极致工艺和尖端装备共同支撑的宏伟大厦。当我们聚焦于玻璃基板(Glass Substrate)和扇出型面板级封装(FOPLP) 这些引领未来的技术时,涂布(Coating)、干燥(Drying)和贴膜(Lamination) 作为其制造流程中不可或缺的核心工艺环节,其设备的性能与精度,直接决定了薄膜的均匀性、界面的结合质量以及最终产品的良率与性能。尤其在处理大尺寸、易翘曲的玻璃基板时,这些工艺面临着均匀性控制、应力管理、产能与效率提升等诸多严峻挑战。

在本次论坛上群翊工業副總经理李志宏主要从玻璃基板及扇出型封装产业趋势、涂布、干燥、贴膜设备于玻璃基板及扇出型封装的应用等方面详述了《涂布、干燥、贴膜工艺设备于玻璃基板及扇出型封装的应用趋势与挑战》。

李志宏副總经理介绍到未来封装越来越复杂,并对比了CoWoS工艺和CoWoP工艺比,CoWoP工艺有产业链企业已经在布局推进中。面板级别的2.5D功能对于持续扩展至关重要。

接着给大家介绍到目前PCB载板化,载板越做越细,导致各阶层界限模糊,很多企业都介入了封装这个板。同时给大家分享了玻璃基的载板及中介层参考规格。

最后给大家介绍了公司目前的布局已经公司可以做的业务板块,公司跨足FOPLP及TGV制程设备,在FOPLP制程与玻璃基板TGV制程中,确保核心材料如干膜(Dry Film)或保护膜均匀覆盖于IC载板与玻璃IC载板上。目前「群翊工业」已经进行多次压膜测试,不仅帮客户厘清实作上的疑虑,还进一步找出适配材料的最佳参数。高精度压膜有效避免气泡、异物缺陷,提高整体制程稳定性与产品可靠性。

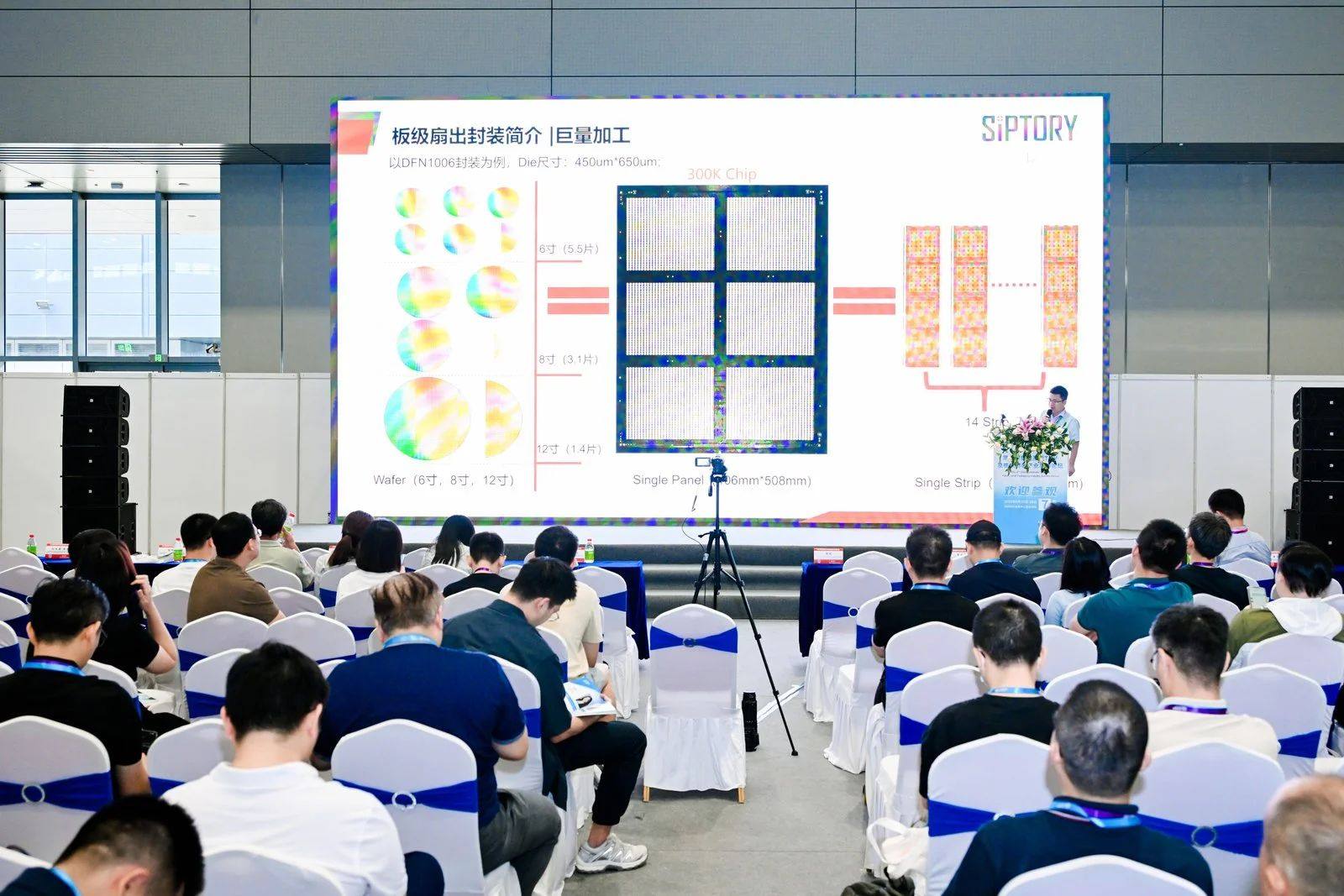

9、《板级扇出封装在功率芯片及模组上的应用》

深圳中科四合科技有限公司 市场总监 赵铁良

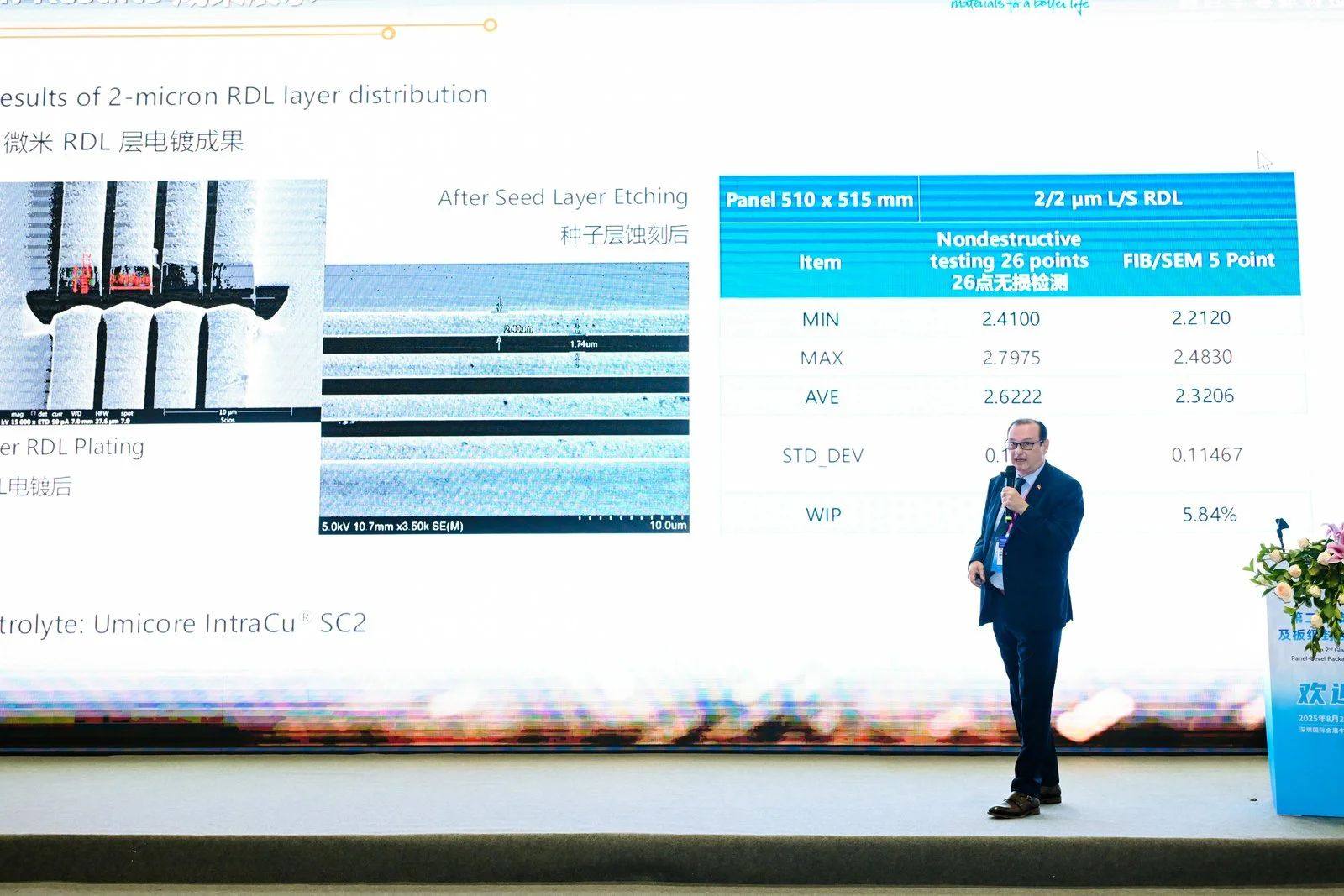

10、《玻璃通孔电镀:单片制程平台》

Plating of Through-Glass-Vias:Single Panel Processing Platform

鑫巨(深圳)半导体科技有限公司 CTO 马库思·郎

IC载板行业是整个半导体生态系统的基础,在这一领域的创新和进步直接影响着最终电子产品的性能、可靠性和效率。TGV 具有众多优势,包括高电气性能、更好的热管理以及显著的微型化潜力,但是要在实际产品中实现上述优点充满了技术和制造的挑战,作为载板材料,玻璃具有独特的优势,例如出色的电绝缘特性、高介电常数以及与传统有机材料相比更好的CTE 值,然而,玻璃的脆性也带来了巨大的挑战。要确保玻璃基板在从通孔成型、金属化到最终的通孔填充各个制造阶段中的机械完整性,需要创新技术方案和对加工参数的精确控制。

鑫巨半导体CTO马库思·郎《玻璃通孔电镀:单片制程平台》报告阐述了玻璃通孔过程中遇到的挑战。通孔形成工艺本身就存在一系列技术障碍,激光钻孔、深反应离子蚀刻 (DRIE)和湿化学蚀刻等技术都面临着各自的挑战,包括通过实现所需的通孔轮廓以达到较低介质损耗因子(Df);玻璃通孔的另一个挑战是金属化,要确保这些通孔内可靠的低电阻电气连接,就必须采用先进的沉积技术,必须对物理气相沉积(PVD)、化学气相沉积(CVD)和电镀等工艺进行优化,以实现通孔内金属层的均匀覆盖和牢固附着。

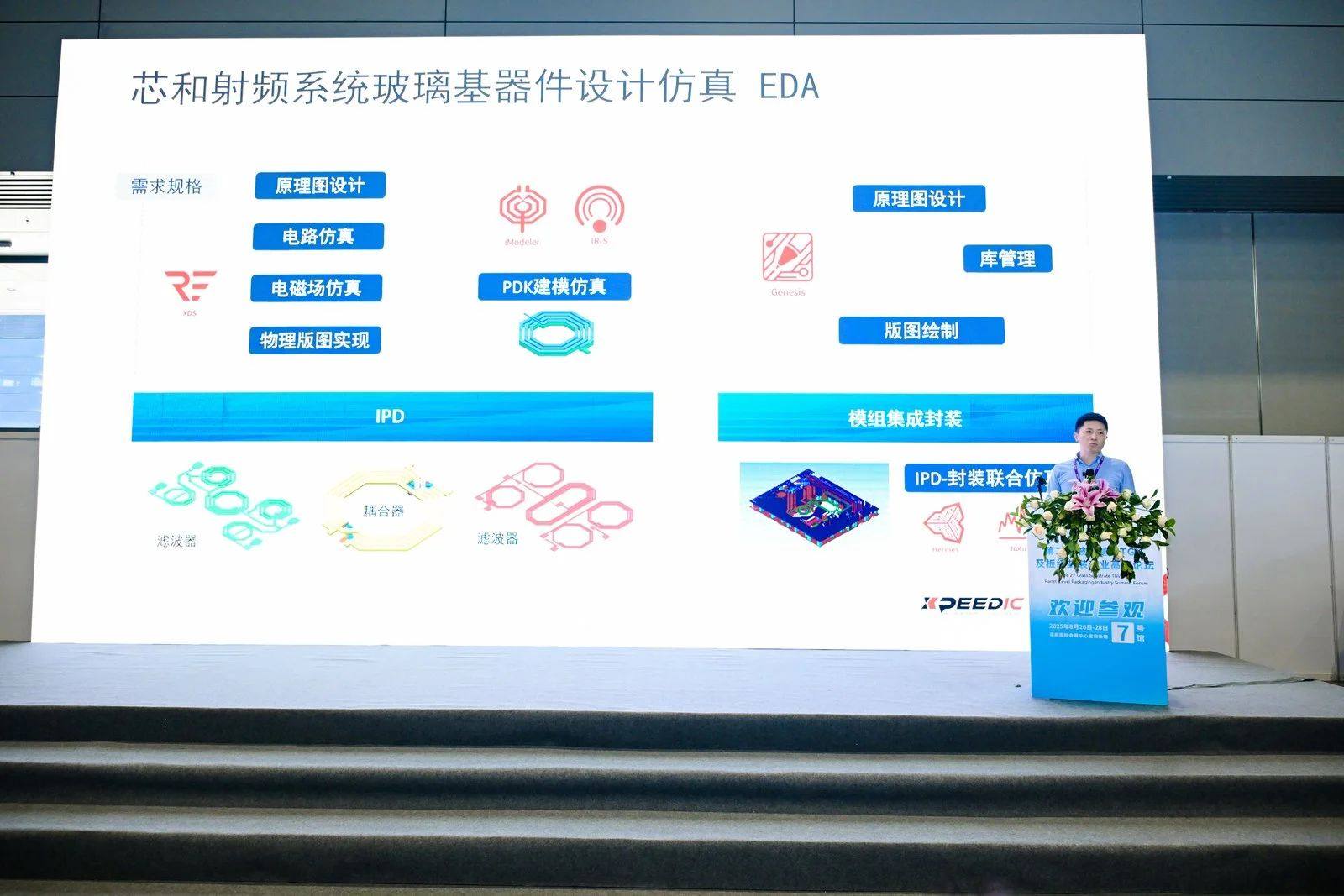

11、《EDA 加速玻璃基器件设计与应用》

芯和半导体科技(上海)股份有限公司 黄晓波 博士

电子集成系统推动数字智能世界的实现,5G/5.5G 连接万物,射频前端影响无线信号质量。无线通信模块包含天线、射频前端、主芯片等部分,用于信号发射/接收过程中的二进制信号与电磁波信号的转换。随着射频前端模组化、高频化、小型化,无源集成器件 IPD 满足射频前端高频率和大带宽应用场景。相比于LTCC和高阻硅工艺,基于玻璃基 TGV的 IPD 更易实现高性能,小体积,高稳定可靠等。

芯和半导体黄晓波博士《EDA 加速玻璃基器件设计与应用》中报告介绍了芯和射频系统玻璃基器件设计仿真 EDA,还有设计案例:基于 TGV 的射频前端 IPD 滤波器。芯和半导体面向 IPD的设计开发提供一站式 EDA解决方案,实现多物理场协同仿真和流程自动化,并独创 IPD-on-Demand 商业模式,覆盖射频前端的IPD的定制化服务与产品组合,帮助缩短 IPD 研发周期,加速 IPD 产品上市。

12、《板级封装在高功率密度集成模块上的应用研究》

天芯互联科技有限公司 器件产品线总监 宋关强先生

天芯互联器件产品线总监宋关强先生在《板级封装在高功率密度集成模块上的应用研究》中阐述了高功率密度的模块需求、基础工艺研究和板级封装案列。

模块封装发展方向是集成化、小型化,功率器件发展方向是高功率密度、模块化,高功率密度模块应用在电动汽车主逆变器、服务器的供电模块等场景。本次演讲天芯互联还介绍了板级封装的技术来源和平台能力,依托PCB工艺平台打造的板级封装,聚焦在功率类产品,I/O pitch>180μm,工艺优势在于载流和散热。板级封装采用铜柱芯片互联方式和双面Heat-sink散热方式。工艺研究方面,天芯互联提到了可靠性问题_盲孔热/机械性能研究,合理的RDL结构设计可以减少FOPLP封装在热冲击条件下的累积应力,这将抑制导通电阻的增加,提高器件封装的可靠性。通流上,孔变槽,增加铜柱与芯片接触面积,以及芯片互联层增加铜厚。散热上,底部通过散热热沉衬底能够快速地将热量散发到周围环境中,以保持器件的工作温度在安全范围内,而顶部通过铜柱散到表面。

二、展会现场图集

明日上午的论坛主题依旧是板级封装,一共4个议题,现场同样汇集了板级封装领域拥有数十年技术经验的专家教授及企业代表,欢迎大家一起期待明日的报告分享。

|

8月28号(板级封装) |

||

|

10:00-10:25 |

面向多芯粒异构先进封装的全玻璃多层互联叠构载板技术 |

沃格集团湖北通格微沃格光电半导体SBU总经理 魏炳义 |

|

10:25-10:50 |

TGV&PLP封装中的聚合物材料以及国产化前景 |

深圳先进电子材料国际创新研究院研发工程师林志强博士 |

|

10:50-11:15 |

玻璃基板光电合封技术 |

厦门云天半导体科技有限公司高级经理伍恒 |

|

11:15-11:40 |

玻璃基板封装关键工艺研究 |

中科岛晶产品经理徐椿景 |