Chiplet 最近经常出现在新闻中。基于小芯片的架构具有多种优势,芯片设计人员在向市场推出新产品时可以从中受益。多年来,系统设计人员将越来越多的功能集成到片上系统(SoC) 中。因此,SoC 的尺寸不断增大。尽管 SoC 在性能方面具有多项优势,但它们也有一个很大的缺点。缺点是随着芯片尺寸不断增大,芯片的良率会受到显着影响。如今,一些最新的SoC 已几乎达到光罩的极限。如此大的芯片尺寸通常会导致产品产量非常低。小芯片提供了具有更小芯片尺寸的解决方案。

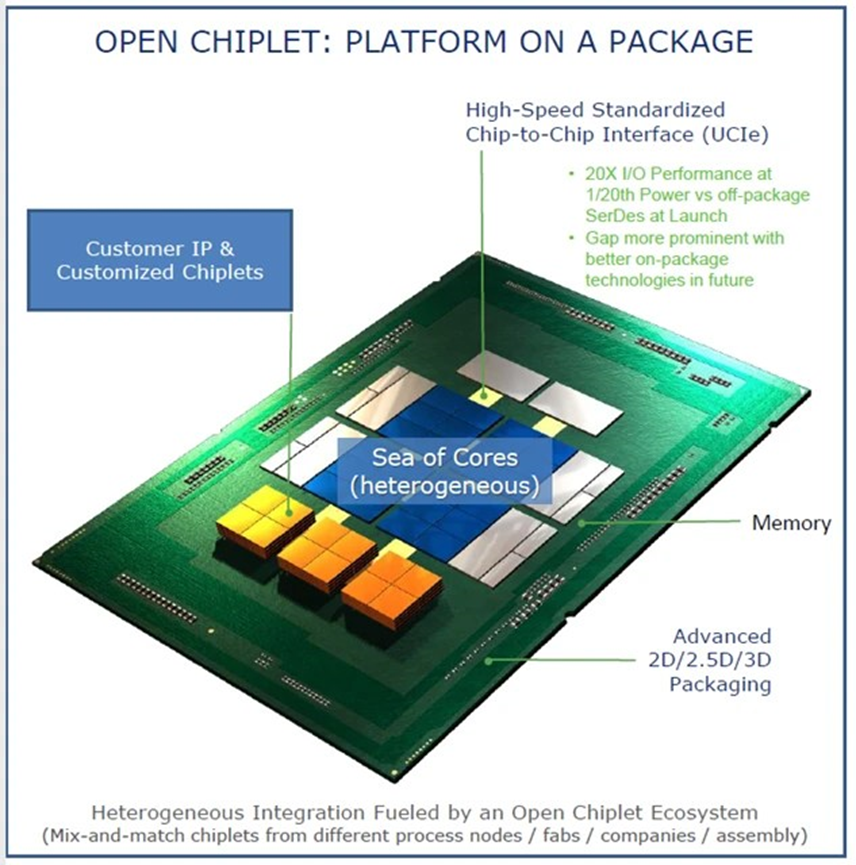

图 1:封装上的开放小芯片平台。资料来源:UCIe 联盟。

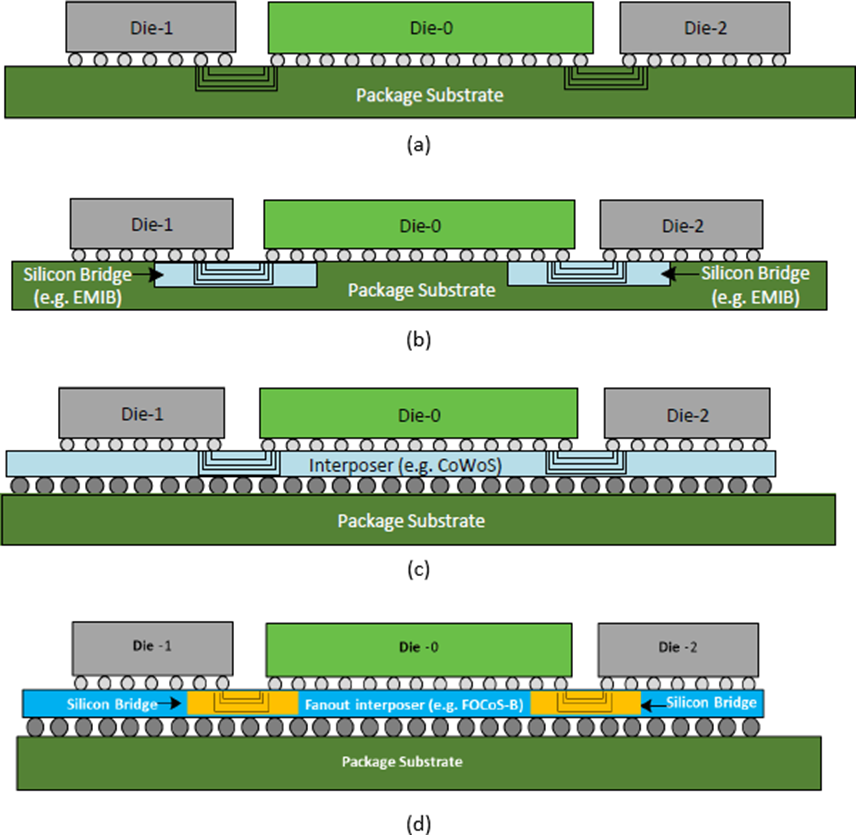

小芯片还可以缩短解决方案的上市时间。系统设计人员可以在小芯片架构中使用来自不同工艺节点和不同技术的不同芯片。这种灵活性是 SoC 所不具备的。基于小芯片的架构还允许对给定解决方案使用最合适的技术,而无需在同一芯片上组合不同技术的复杂性。使用来自不同供应商的不同模具还可以降低开发成本,因为它允许使用现成的现成设计,而不是集成新产品。通常,与更大的 SoC 相比,它还能带来更好的良率。很多时候,这样的解决方案也是可定制的。因此,针对不同的要求,客户可以使用或调整解决方案以获得最佳性能。市场上有不同类型的小芯片架构解决方案。例如,小芯片可以是基于基板(图 2a)、基于硅桥(图 2b)、基于中介层(图 2c)或基于重分布层 (RDL) 的设计(图 2d)。

图 2:不同的小芯片设计方法。资料来源:UCIe 联盟

对于芯片设计者来说,小芯片架构并不一定是万能的。它也面临着一系列挑战。每当一个设计团队使用多种不同的硅源配置异构解决方案并由其他人进行组装时,分配整个解决方案的所有权都是一项挑战。任何此类解决方案都需要进行模拟,其中包括不同的工艺节点——也许完全是不同的硅技术和组装工艺。当集成设备制造商 (IDM) 设计自己的多芯片模块 (MCM) 时,他们可以控制 I/O 的位置以及两个芯片之间的连接路径。对于小芯片,不同供应商之间的接口和 I/O 可能未针对功耗或噪声进行优化。

越来越多的供应商开始关注其产品的安全问题。使用 IDM,安装安全措施是可以管理的,因为对测试和封装地点的进入可以限制。对于小芯片来说,确保安全程序要困难得多,因为制造过程中涉及更多参与者,并且一路上有更多接触点。

功率是另一个考虑因素。最新上市的硅产品增加了功耗。在当今的应用中,管理热特性并了解解决方案的总功耗非常重要。方案中的某些部分可能会散发更多热量。不同的小芯片可能具有不同的芯片厚度。最后,使用不同的热界面材料从整个解决方案中抽掉热量非常重要。目前尚不清楚小芯片解决方案的热管理方面将如何处理。如果小芯片是专门为单一应用或目的而设计的,它就会失去小芯片架构的一个关键优势——它变成了类似于 IDM 已经在做的定制解决方案。

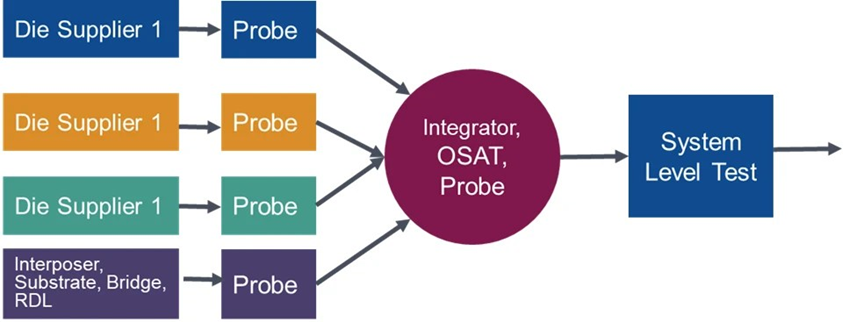

Chiplet甚至更加复杂,因为不同的芯片供应商可能会提供 SoC、内存、I/O 或ASIC。接下来,如果是基于RDL的解决方案,则有单独的基板或中介层供应商。最后,可能会与 OSAT 或晶圆厂进行合作。使用新的嵌入式桥结构,可能会增加一层额外的复杂性。此外,集成商将采购所有这些不同的材料,然后将解决方案封装在一起。结果,这种解决方案的复杂性呈指数级增长。在多芯片组装的情况下,每个步骤都涉及测试程序。芯片供应商测试芯片并提供KGD Mapping (known good die)。封装开始后,每个阶段都可能需要某种芯片测试或颗粒测试,以确保组件仍然有效。产品组装结束后,需要进行系统级测试(SLT)以确保整个系统按设计运行。因此,供应链变得复杂,更多的参与者参与小芯片组装。随着行业开发这些解决方案并在市场上获得越来越多的关注,明确定义谁向谁提供什么、可交付成果是什么以及如何解决出现的问题非常重要。参见图3。

图 3:生态系统框图。

在任何业务决策中,解决方案的成本对产品的可行性都有重大影响。如果这样的解决方案成本过高,那么它就不会在市场上取得成功。周期时间是许多小芯片供应商正在考虑的另一个考虑因素。如果最终产品的封装是在不同的地方而不是在一个屋檐下完成,那么周期时间就会受到影响。它还可能导致更高的封装成本。如今大多数基于小芯片的设计都是针对成本敏感度较低的数据中心。对于成本更敏感的应用,例如消费类或汽车应用,需要考虑更多的设计方面,以使整个装配成本具有竞争力。

目前市场上已有 Chiplet 解决方案。然而,这些仍然是定制设计——而不是人们可以从商品市场获得来构建产品的现成部件。为了让小芯片真正取得成功,互操作性和标准化是必须具备的。UCIe 联盟正在努力实现这一目标,未来几年将决定这些努力的成功与否。

原文始发于微信公众号(安靠上海):赋能Chiplet 供应链