摘要:塑封制程中的芯片偏移量一直是板级扇出型封装(FOPLP)技术面临的巨大挑战。在介绍现有FOPLP技术工艺的基础上,通过分析塑封制程中产生芯片偏移量的原因,借鉴华天科技的嵌入式硅基扇出(eSiFO)封装技术,提出了3种能有效减小FOPLP中芯片偏移量的方法,即凹槽型塑封结构方法、贯穿型塑封结构方法和光阻围堰型封装结构方法。凹槽型和贯穿型塑封结构方法通过制备带凹槽或贯穿结构的板级塑封样品,将芯片粘贴在凹槽结构或贯穿结构内,再配合真空压膜工艺来达到减小FOPLP中芯片偏移量的目的。光阻围堰型封装结构方法利用光阻在承载板上形成光阻围堰结构,将芯片粘贴在光阻围堰结构内,以达到减小FOPLP中芯片偏移量的目的。艾邦建有玻璃基板与TGV技术交流群,欢迎您加入共享资源,交流经验。

0 引言

板级扇出型封装(FOPLP)是一种先进的芯片封装技术,与晶圆级扇出型封装(FOWLP)技术相对应。在FOPLP技术中,芯片封装不再以晶圆为载体,而是使用面板作为封装基板,这些面板采用金属、玻璃或高分子聚合物材料制成。FOPLP技术可以看作是FOWLP技术的延伸,它能实现在更大的方形载板上进行扇出型封装制程,其优势在于可以在更大的面积上进行集成电路(IC)的制造,相较于传统的晶圆级封装,可以显著提高单位面积内的IC产量,从而降低成本并提升产品竞争力。与FOWLP技术相比,FOPLP技术有望显著降低组装成本,因为其整合了芯片放置、成型和重布线层(RDL)形成的相关工艺,可以在同等良率的情况下实现按比例放大。FOPLP技术是一种从晶圆和条带级向更大尺寸面板级转换的方案,由于其潜在的成本效益和更高的制造效率,目前已吸引了市场的广泛关注。许多不同商业模式的厂商,例如外包半导体组装和测试厂商、集成器件制造商、代工厂、基板制造商及平板显示厂商,均已经开始涉足板级封装业务。由于面板的大尺寸和更高的载具使用率(95%),该技术带来了远高于FOWLP技术的规模经济效益,并且能够实现大型封装的批量生产。

本文首先介绍了现有FOPLP技术工艺流程,主要包括基于Chip First (Face-Down/Face-Up)工艺和基于Chip Last工艺的FOPLP技术,分析FOPLP技术中芯片在塑封制程中产生偏移量的原因,并介绍现有的解决办法。最后,通过借鉴华天科技的eSiFO封装技术, 提出了3种能有效减小FOPLP技术中芯片偏移量的可行方法,即凹槽型塑封结构方法、贯穿型塑封结构方法和光阻围堰型封装结构方法。

1 FOPLP工艺介绍

FOPLP技术主要有芯片优先(ChipFirst)和金属线路优先(RDLFirst,也叫Chip Last)2种方法,ChipFirst又分为芯片面朝上(Face-Up)和芯片面朝下(Face-Down) 2 种工艺。 Face-Down 工艺将 RDL/UBM层直接连接到焊料凸块上,而Face-Up工艺则使用铜柱凸块作为RDL/UBM互连的第一层,从而允许更小的I/O端间距[15-10。作为构建扇出RDL中介层的首选替代方案,ChipLast技术正在兴起,扇出RDL中介层作为比硅中介层成本更低的解决方案,被广泛应用于封装高性能芯片(CPU、GPU、FPGA等),日益受到业界关注。

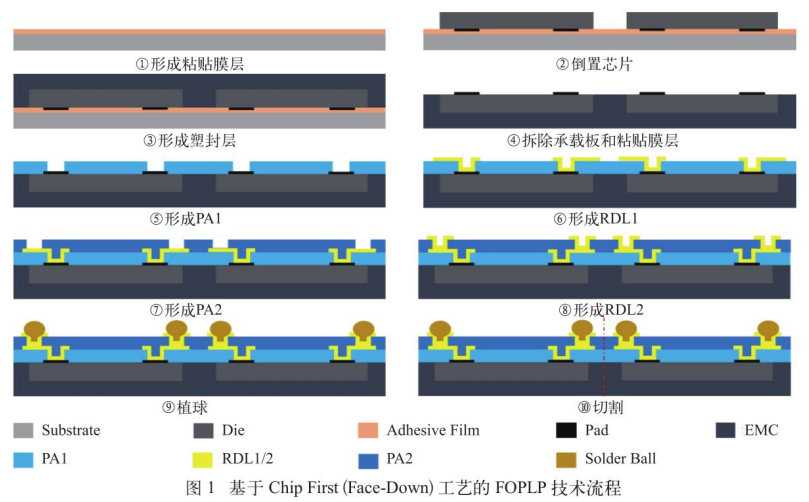

基于Chip First (Face-Down)工艺的FOPLP技术流程如图1所示,主要包含10个步骤:1)在承载板上形成粘贴膜层;2)将减薄、切割后的芯片正面朝下粘贴在承载板上;3)在芯片背面形成塑封层;4)拆除承载板和粘贴膜层;5)形成带通孔结构的第一绝缘层(PA1);6)形成第一金属重布线层(RDL1);7)形成带通孔结构的第二绝缘层(PA2);8)形成第二金属重布线层(RDL2);9)完成植球工艺;10)切割。

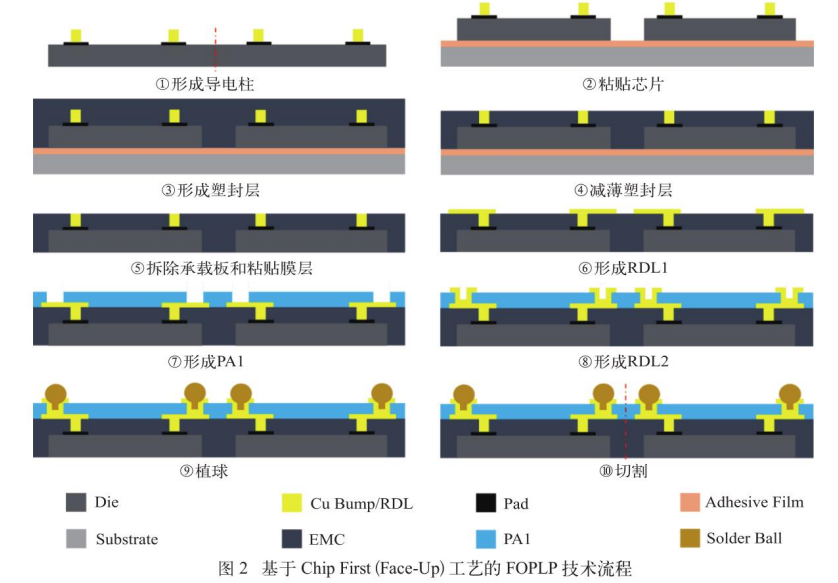

基于ChipFirst (Face-Up)工艺的FOPLP技术流程如图2所示,主要包含10个步骤:1)在芯片焊盘上形成金属导电柱;2)将减薄、切割后的芯片正面朝上粘贴在承载板上;3)在芯片正面形成塑封层;4)减薄塑封层;5)拆除承载板和粘贴膜层;6)形成RDL1;7)形成 PA1;8)形成RDL2;9)完成植球工艺;10)切割。

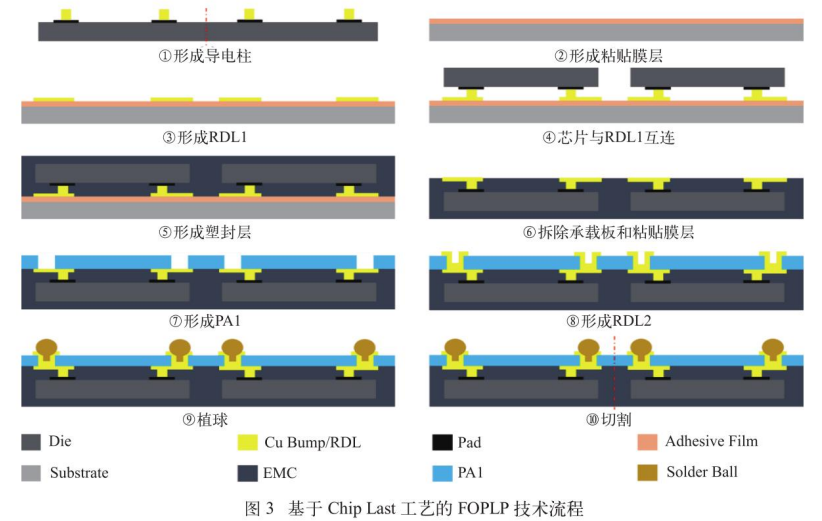

基于ChipLast工艺的FOPLP技术流程如图3所示,主要包含10个步骤:1)在芯片焊盘上形成金属导电柱;2)在承载板上形成粘贴膜层;3)在粘贴膜层上形成RDL1;4)将减薄、切割后的芯片与承载板上的RDL1互连;5)在芯片背面形成板级塑封层;6)拆除承 载板和粘贴膜层;7)形成PA1;8)形成RDL2;9)完成 植球工艺;10)切割。

2 芯片偏移量的产生及解决方案

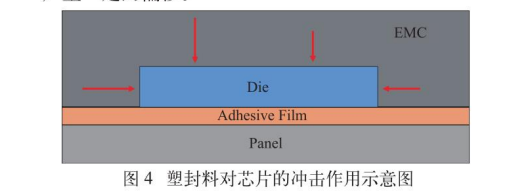

基于 Chip First(Face-Down/Face-Up)工艺的FOPLP技术流程中,最重要的环节为塑封。通过塑封环节可以成功地将芯片封装的作业单元从晶圆样品(尺寸为8英寸或12英寸)转变为板级样品(尺寸为500 mm×500 mm、500 mm×650 mm 及 600 mm×600mm),从而提高载具使用率、大幅度降低制程生产与材料的成本。塑封也是对FOPLP造成最大挑战的环节,主要表现为流动的塑封料在塑封制程中会对粘贴在承载板上的芯片产生较大的冲击,导致芯片产生较大的位移,不利于后续制程特别是光刻制程的顺利进行。图4为塑封料对芯片的冲击作用示意图,在塑封过程中,芯片会受到来自水平和垂直方向的冲击力,当芯片在水平或垂直方向上受力不均匀时,就会产生一定的偏移。

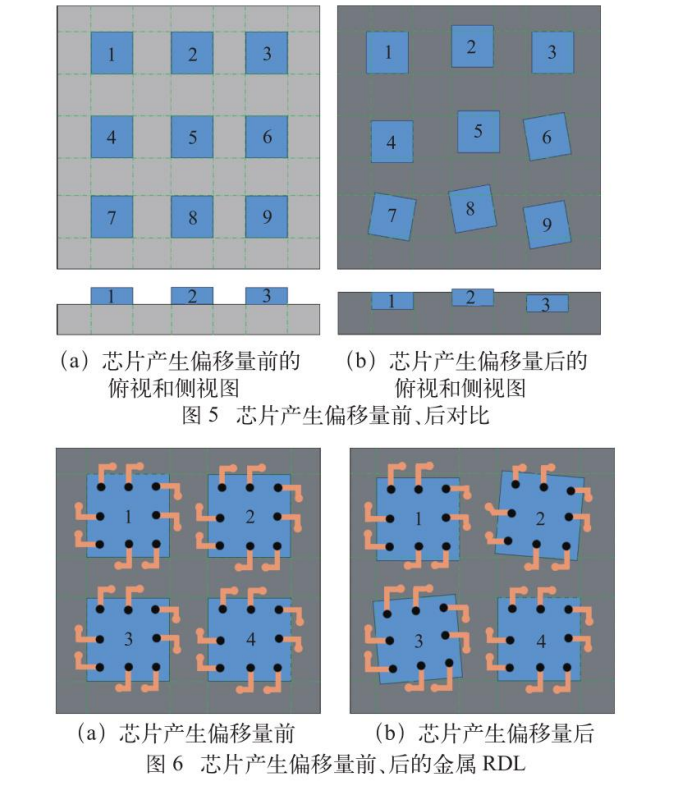

在塑封过程中,由于不同芯片受到的冲击力不同,导致板级塑封样品上每个芯片的偏移量(偏移距离、偏移方向、偏移/旋转程度等不同。芯片产生偏移量之前,板级塑封样品上每颗芯片的位置在水平方向上呈现规律性分布,在垂直方向上的位置高度呈现出一致性分布,如图5(a)所示。经过塑封后,每颗芯片的偏移量都不一样,有的芯片仅存在水平方向上的偏移量(东/南/西/北/东北/东南/西南/西北等不同方向的偏移),有的芯片仅存在垂直方向上的偏移量(上/下偏移),有的芯片仅存在旋转偏移量(顺时针/逆时针偏移),有的芯片存在水平、垂直、旋转中的2种或3种组合式的偏移量,这就导致同一个板级塑封样品中,每颗芯片上相同位置的导电结构呈现出完全无规律性的分布模式,如图5(b)所示。图6(a)为芯片产生偏移量前的金属RDL示意图,板级塑封样品上每颗芯片相同位置的导电结构呈现出规律性分布,保证了封装后续制程(特别是光刻制程)能顺利进行。但经过塑封后的板级塑封样品上每颗芯片的偏移量均不一样,此时每颗芯片上相同位置的导电结构呈现出完全无规律性的分布,导致后续制程中确保通孔结构位置与每颗芯片的导电结构位置相匹配变得异常复杂,甚至无法进行有效的光刻或金属RDL制程。

解决芯片在塑封制程中产生偏移量的现有办法主要是通过自动光学检测(AOI)和二次金属RDL规划的结合来实现的,即完成塑封制程的板级塑封样品首先经过一道AOI,以准确收集板级塑封样品上每颗芯片的导电结构经偏移后的新位置坐标,新位置坐标经软件处理后输出新的曝光文件(与新的金属RDL相对应),后续光刻制程按照新的曝光文件进行相关作业。

需要注意的是,新的金属RDL末端位置(未与芯片导电结构相连的RDL端)与旧的金属RDL末端位置(芯片产生偏移量后的金属RDL端)必须保持相同,如图6 (b)所示。纠正 FOPLP中芯片在塑封过程中产生偏移量的现有方法较为复杂,不利于FOPLP技术的推广普及。

3 有效减小芯片偏移量的方法

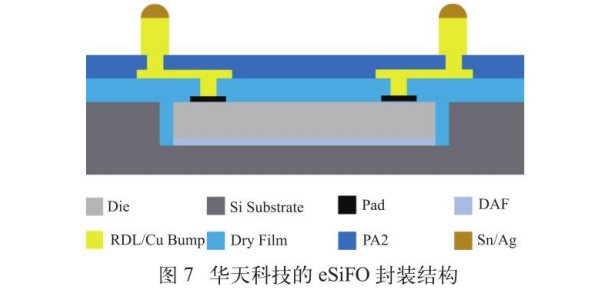

华天科技于2018年成功开发具有自主知识产权的eSiFO封装技术,该技术具有支持多芯片封装、可以实现超大尺寸、超薄的封装结构以及高密度扇出等特点。与使用模塑料塑封不同,eSiFO封装技术使用硅基板为载体,通过在硅基板上千法刻蚀形成凹槽,将芯片正面向上放置且固定于凹槽内,然后采用真空压膜技术填补支撑片与芯片之间的空隙。芯片表面和硅圆片表面构成了一个扇出结构,在这个扇出结构上可以进行多层布线并制作引出端焊球,然后对其进行切割、分离和封装。

eSiFO封装结构如图7所示,利用黏性膜(DAF)将芯片固定在硅基凹槽内,硅基凹槽与芯片之间会形成间隙,真空压膜技术利用干膜填充间隙,由于干膜对芯片的冲击力较小,因此能有效地减小芯片偏移量。并且在将芯片正面朝上放置在硅基凹槽的过程中,由于贴片机的高精度特性,芯片在DA(Die Attach)过程中自身产生的偏移量较小且在可控范围内;由于芯片四周有硅基凹槽的限制,芯片在干膜粘贴过程中受到冲击力作用时偏移量可忽略。相较于传统的eWLB封装,eSiFO封装的成本更低,翘曲更小,能有效解决塑封过程中存在的芯片偏移量问题,同时具有较好的热管理能力。

参考华天科技的eSiFO封装技术,以下介绍3种能有效减小FOPLP塑封制程中产生芯片偏移量的方法。根据板级封装结构的不同,将这3种板级封装结构命名为凹槽型塑封结构、贯穿型塑封结构和光阻围堰型封装结构。

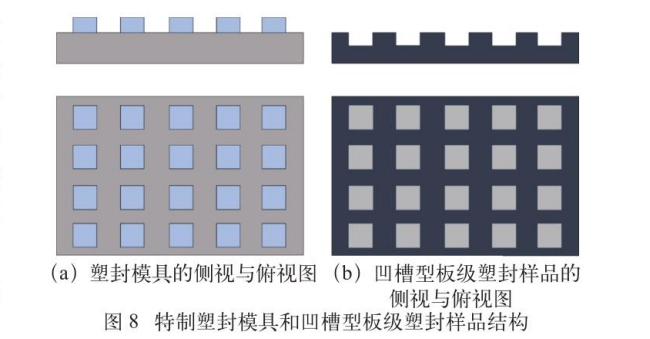

3.1 凹槽型塑封结构方法

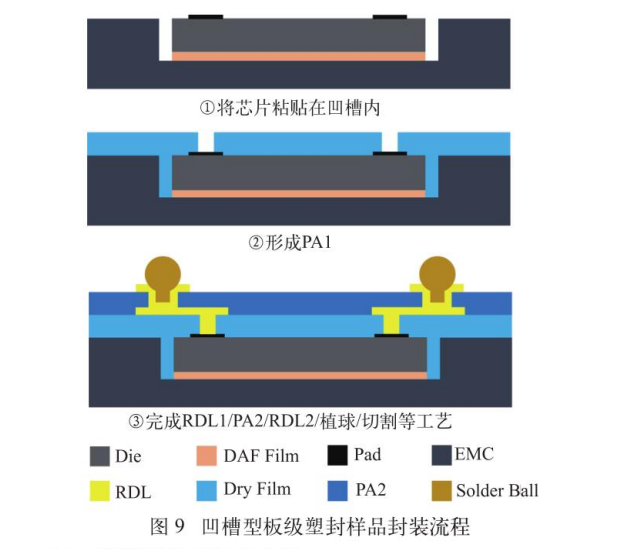

利用凹槽型塑封结构有效减小FOPLP中芯片偏移量的关键是制备带凹槽结构的板级塑封样品和采用真空压膜技术来填充空隙。通过在塑封制程中使用特制的塑封模具可以制备出带凹槽结构的板级塑封样品,特制塑封模具如图8(a)所示,该模具的上表面存在一定数量的形状规则的突出小块,突出小块的尺寸与待封装芯片的尺寸相匹配(通常略大于待封装芯片的尺寸),小块的数量与拟在板级塑封样品表面包埋的芯片数量相对应,小块的高度与待封装芯片的厚度相匹配(通常略大于待封装芯片的厚度)。特制塑封模具的尺寸与拟制备板级塑封样品的尺寸相对应。使用特制塑封模具得到的凹槽型板级塑封样品结构如图8 (b)所示,其上会形成一定数量的凹槽结构。

带凹槽结构的板级塑封样品封装流程如图9所示,主要包含3个步骤:1)利用DAF将芯片正面朝上粘贴在板级塑封样品的凹槽结构内,凹槽与芯片之间会形成间隙;2)采用真空压膜技术来填充凹槽与芯片之间的间隙,形成带通孔结构的PA1;3)在PA1上完成RDL1/PA2/RDL2/植球/切割等工艺。与华天科技的eSiFO封装技术类似,在将芯片正面朝上放置在板级塑封样品凹槽的过程中,由于贴片机的高精度特性,芯片在DA过程中自身产生的偏移量较小且在可控范围内。在真空压膜过程中,由于芯片四周有凹槽的限制,芯片在干膜粘贴过程中受到冲击力作用时偏移量可忽略,从而达到有效减小芯片偏移量的目的。

3.2 贯穿型塑封结构方法

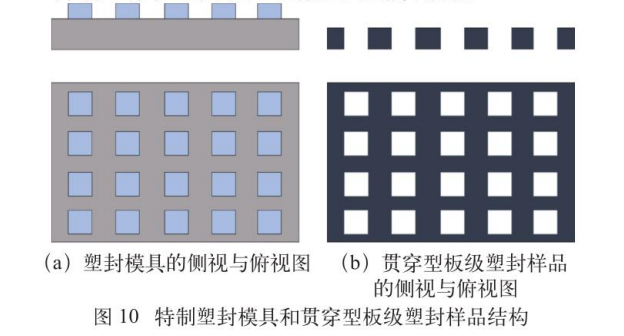

利用贯穿型塑封结构有效减小FOPLP中芯片偏移量的关键是制备带贯穿结构的板级塑封样品和采用真空压膜技术来填充空隙。通过在塑封制程中使用特制的塑封模具可以制备出带贯穿结构的板级塑封样品,特质塑封模具结构如图10(a)所示,该模具的上表面有一定数量形状规则的突出小块,小块的尺寸与待封装芯片的尺寸相匹配(通常略大于芯片尺寸),小 块数量与拟在板级塑封样品表面包埋的芯片数量相 对应,小块高度与待封装芯片的厚度相对应。特制塑 封模具的尺寸与拟制备板级塑封样品的尺寸相对应。 使用特制塑封模具得到的板级塑封样品结构如图10 (b)所示,其上会形成一定数量的贯穿结构。

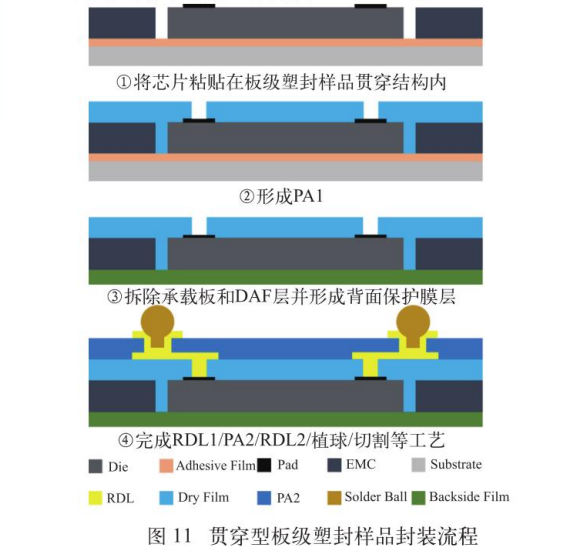

带贯穿结构的板级塑封样品封装流程如图11所示,主要包含4个步骤:1)将带贯穿结构的板级塑封样品粘贴在承载板上,将芯片正面朝上粘贴在贯穿结构内,此时贯穿结构与芯片之间会形成间隙;2)采用真空压膜技术填充贯穿结构与芯片之间的间隙,形成带通孔结构的PA1;3)将承载板和DAF层从板级塑封样品的背面拆除,在板级塑封样品背面形成新的背面保护膜层;4)在PA1上完成RDL1/PA2/RDL2/植球/切割等工艺。与eSiFO封装技术类似,将芯片正面朝上放置在板级塑封样品贯穿结构的过程中,由于贴片机的高精度特性,芯片在DA过程中自身产生的偏移量较小且在可控范围内,在真空压膜过程中由于芯片四周有贯穿结构的限制,芯片在干膜粘贴过程中受到冲击力作用时偏移量可忽略,从而达到有效减小芯片偏移量的目的。

3.3 光阻围堰型封装结构方法

利用光阻围堰型封装结构有效减小FOPLP中芯片偏移量的关键是光阻围堰结构的制备。在带DAF层的承载板上制备的光阻围堰结构的尺寸与待封装芯片的尺寸相匹配(通常略大于芯片尺寸),光阻围堰结构的数量与拟在板级塑封样品表面包埋的芯片数量相对应,光阻围堰结构的高度小于待封装芯片的厚度。该结构方法已于2022年申请相关专利保护,申请公告号为CN115083926A。

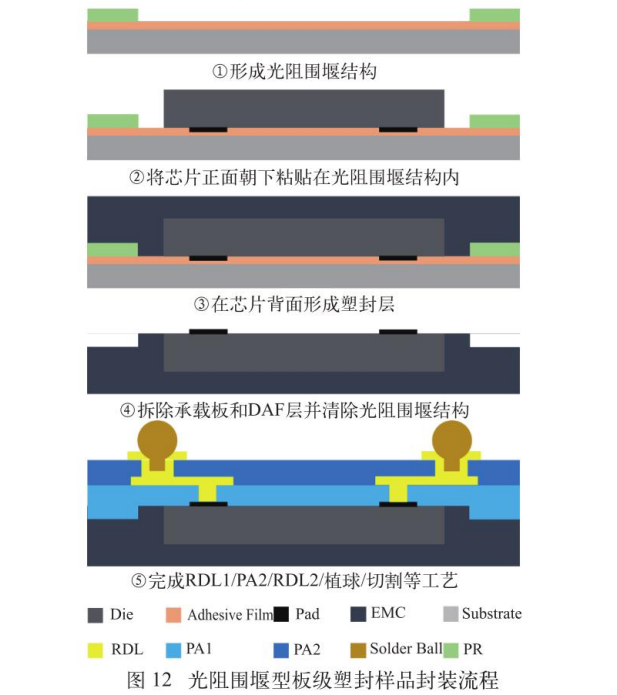

光阻围堰型板级塑封样品封装流程如图12所示,主要包含5个步骤:1)在带DAF层的承载板上形成光阻围堰结构;2)将芯片正面朝下粘贴在承载板上的光阻围堰结构内,此时在光阻围堰结构与芯片之间会形成间隙;3)在芯片背面形成塑封层;4)拆除承载板和DAF层并清除光阻围堰结构;5)在板级塑封样品上完成PA1/RDL1/PA2/RDL2/植球/切割等工艺。与eSiFO封装技术类似,将芯片正面朝下放置在光阻围堰结构的过程中,由于贴片机的高精度特性,芯片在DA过程中自身产生的偏移量较小且在可控范围内,塑封过程中由于芯片四周有光阻围堰结构的限制,芯片在受到塑封料产生的冲击力作用时偏移量可忽略,从而达到有效减小芯片偏移量的目的。

4 结论

借鉴华天科技的e-SiFO封装技术中有效减小芯片偏移量的关键工艺,本文介绍了3种能有效减小FOPLP封装中芯片偏移量的封装结构及方法。其中,通过塑封工艺制备的凹槽结构和贯穿结构以及通过光刻工艺制备的光阻围堰结构均能有效减小芯片偏移量,这为FOPLP技术在封装领域的普及提供了技术保障。当前工作尚缺少相关的仿真验证和工艺流片验证作为支撑,课题组后续将进一步开展相关研究,力争为FOPLP技术的工艺优化提供更好、更完善的技术支持。

来源:电子与封装

刘吉康(湖北第二师范学院物理与机电工程学院,武汉430205)

D0I: 10.16257/j.cnki.1681-1070.2024.0170

艾邦建有玻璃基板与TGV技术交流群,可以加强产业链的合作,促成各企业的需求对接,同时您也可以与行业精英共同探讨玻璃基板及TGV技术的前沿动态,共享资源,交流经验,欢迎您的加入。

|

序号 |

议题 |

公司 |

|

1 |

TGV集成三维互联核心材料技术 |

华中科技大学温州先进制造研究院 |

|

2 |

涂布、干燥、贴膜工艺设备于玻璃基板及扇出型封装的应用趋势与挑战 |

群翊工業李志宏副總经理 |

|

3 |

Evatec先进封装基板FOPLP刻蚀和溅射方案 |

Evatec China 技术市场总监 陆原博士 |

|

4 |

TGV玻璃通孔激光加工中的基础问题和极限探究 |

南方科技大学教授徐少林 |

|

5 |

基于SLE(选择性激光蚀刻)工艺的精密玻璃加工——机遇、挑战与解决方案 |

Workshop of Photonics/凌云光技术股份有限公司 (VP of Business Development and Innovation) Martynas Dagys |

|

6 |

基于Holotomography(HT)的玻璃基板三维无损检测与良率提升策略 |

韩国Tomocube 销售经理 金泳周 |

|

7 |

玻璃基板封装关键工艺研究 |

中科岛晶产品经理徐椿景 |

|

8 |

Next in Advanced Packaging: Why Glass Core Substrates is emerging |

YOLE Bilal HACHEMI |

|

9 |

面向玻璃基板的先进封装解决方案 |

钛昇 |

|

10 |

玻璃基板原材料的技术及其应用 |

拓科达科技(深圳)有限公司/NEG 日本电气硝子 |

|

11 |

应用于三维封装的PVD 系统 |

深圳市矩阵多元科技有限公司董事长张晓军 |

|

12 |

议题拟定中 |

Mitutoyo三丰精密量仪(上海)有限公司 |

|

13 |

议题拟定中 |

成都奕成科技股份有限公司 |

|

14 |

议题拟定中 |

希盟科技 |

|

15 |

议题拟定中 |

牛尾贸易(上海)有限公司 |

|

16 |

议题拟定中 |

芯和半导体科技(上海)有限公司 |

|

17 |

议题拟定中 |

施密德集团公司SCHMID Group N.V. |

|

18 |

TGV玻璃核心技术的挑战与解决方案 |

拟邀广东佛智芯微电子技术研究有限公司 |

|

19 |

玻璃基板先进封装技术发展与展望 |

拟邀东南大学 |

|

20 |

三维封装硅通孔与玻璃通孔技术发展及应用 |

拟邀厦门云天半导体科技有限公司 |

加微信李小姐:18823755657(同微信)

邮箱:lirongrong@aibang.com

扫码添加微信,咨询会议详情

注意:每位参会者均需要提供信息

方式二:长按二维码扫码在线登记报名

或者复制网址到浏览器后,微信注册报名

https://www.aibang360.com/m/100255?ref=172672