多年来,人们一直在探讨一种面板级 (PL) 扇出型 (FO) 封装方法,以降低基于重分布层 (RDL) 技术的先芯片扇出型 (FO) 封装的成本。最近,多层高密度后芯片封装已被引入用于更先进的应用。该技术也受益于面板级 (PL) 工艺,从而降低成本。由于封装尺寸较大,应用处理器 (AP) 或多芯片模块 (MCM) 等应用将比典型的先芯片扇出型 (FO) 封装中较小的电源管理集成电路 (PMIC)、收发器或音频编解码器应用受益更大。

面板级扇出型 (PLFO) 封装的已知技术挑战包括:整块面板的芯片移位、工艺流程中面板的翘曲(这会限制重新分布层的数量),以及控制面板级背研磨工艺中的总厚度变化 (TTV)。面板级设备的资本支出以及面板生产线的填充难度等商业因素是主要的财务考虑因素。

本次展示了一项 650mm x 650mm PLFO 技术,该技术能够在一块载板上组装四个 300mm圆形或 300mm方形扇出子面板。该技术能够重复利用重组和芯片/封装级工艺设备,专注于面板工艺,在重新分布层工艺中实现最大的成本效益。使用载板可最大限度地减少翘曲,从而能够在不影响工艺性能的情况下实现更多 RDL 的实施。流程的重组部分在较小的尺寸板上进行,从而最大限度地减少了大面板上芯片偏移的影响。相同的面板设备和基础设施也可用于芯片后置 PLFO 或高密度、高质量的无芯基板。工艺流程细节将基于 PLFO 中试线进行分享。

将展示芯片后扇出测试工具上的组件级可靠性结果,以及芯片先行 PLFO 与 300mm扇出晶圆的比较成本模型,适用于芯片先行和芯片后扇出封装。

为了解决面板生产线填充问题,已经开发出一种柔性面板技术,该技术可以广泛应用于各种封装技术。

技术应用:

- 晶圆级芯片规模封装 (WLCSP) – 300mm、200mm、150mm

- 晶圆级扇出型 (WLFO) – 先芯片,再重分布层 (RDL)

- 系统级封装 (SiP)

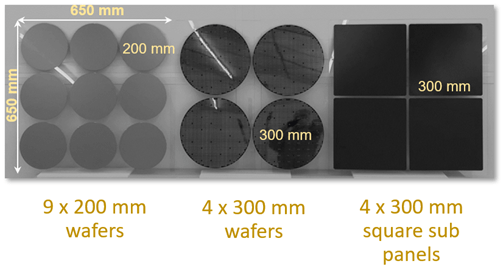

图 1:在 650 毫米 x 650 毫米玻璃面板上组装的晶圆和面板的示例

混合面板级封装(Hybrid PLP)技术(HPLT)基于650mm x 650mm的大尺寸面板。该面板尺寸可处理4片300mm晶圆或方形面板、9片200mm晶圆或16片150mm晶圆。

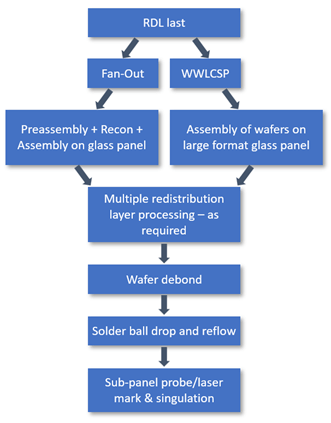

如图 1 所示,对于 WLCSP、先芯片 WLFO 晶圆或面板级扇出型 (PLFO) 面板,在玻璃面板上组装后的工艺流程实际上是相同的。图 2 显示了 WLCSP 和 WLFO 工艺流程的描述。

图 2:WLCSP 和先芯片扇出工艺流程

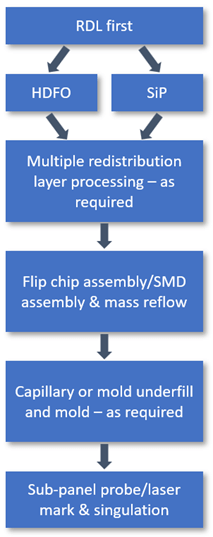

晶圆或子面板通过临时粘合剂组装在热膨胀系数 (CTE) 匹配的大尺寸玻璃面板上。介电层采用适当的逐板工艺应用,以确保出色的层均匀性。曝光在面板级步进设备上进行,对准在单个晶圆或子面板上进行。显影工艺再次逐板执行。固化在气氛控制固化炉中进行。所选物料清单 (BOM) 应具有与晶圆工艺线上加工的重分布层相同的机械和化学特性。对于该技术的后芯片或先 RDL 应用,工艺流程相反,如图 3 所示。

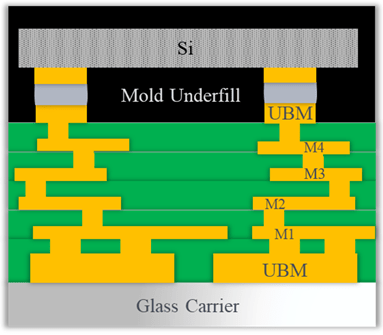

RDL 层直接构建在玻璃面板上,从凸块下金属化层 (UBM) 开始,通过相应的层间电介质从顶部 RDL 层持续到底部 RDL 层。完成底部 RDL 层后,需要额外的 UBM 层,以便将芯片倒装芯片组装到 RDL 堆栈上。倒装芯片组装后,可使用模具底部填充 (MUF) 工艺,或者对于更精细间距的应用,可使用毛细管底部填充 (CUF) 和模具工艺完成器件的封装。然后,可将玻璃面板与成型的器件分离。当前可用的倒装芯片和模具设备要求将玻璃面板细分为更小的尺寸,这意味着玻璃面板无法在此应用中重复使用。使用面板级倒装芯片和成型可以克服这一限制。

图 3:RDL 首次应用的流程

成本

HPLT 专注于所有再分布技术中最昂贵的环节——再分布层本身。其工艺步骤将带来显著的成本效益,即大规模并行处理,这些步骤以面板为基础进行。这些步骤包括:介质层和光刻胶层的涂覆和显影;介质层和光刻胶层的曝光;介质层的固化;种子层的物理气相沉积;电化学沉积;光刻胶剥离;以及剩余种子层的化学湿法蚀刻。

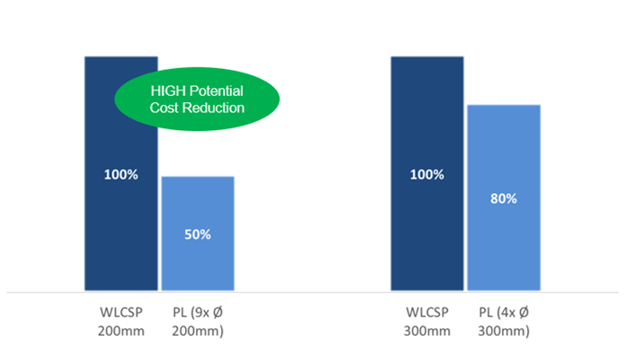

这一策略为所有相关封装技术带来了显著的成本优势。为了准确评估使用该技术可实现的潜在成本收益,我们针对不同的应用进行了成本建模。WLCSP 应用可以进行最直接的比较,因为所有芯片或封装尺寸的考虑因素都可以忽略不计,因为比较中只考虑晶圆级工艺成本。

图 4:晶圆级设计与面板级设计上执行的重新分布层的成本比较

从图 4 中的成本比较可以看出,可以获得显著的成本优势,并且随着浪费面积与有用面积之比的降低,晶圆尺寸越小,成本效益就越高。

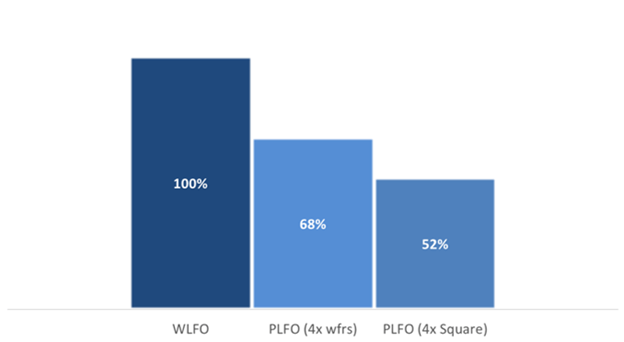

对于扇出型应用,通常考虑先芯片应用,因为后芯片过于依赖后续组装工艺。对于先芯片应用,比较三种情况:在 300mm晶圆加工线上生产的 300mm晶圆上的 WLFO,在 650mm面板上加工和组装的 4 x 300mm圆形晶圆,以及最终在 650mm面板上组装的 300mm方形面板,如图 5 所示。

图 5:对于先芯片应用,晶圆级设计与面板级设计上执行的重新分布层的成本比较

成本模拟显示,在大尺寸面板上组装4块300mm圆形晶圆可带来显著的加工效益。然而,在玻璃面板上组装4块300mm方形子面板,其面积利用率更高,从而带来更显著的潜在效益。

测试车辆描述

为了展示该技术的能力,选择了6层金属层 RDL-first 测试载体 (TV)。

图6:测试车辆结构

多层RDL结构采用光刻工艺构建在650 mm x 650 mm的玻璃板上,如图3所示。在完成RDL工艺直至芯片侧凸块下金属化(UBM)后,玻璃板被切割成更小的块体,以适应后续组装设备的工艺能力。采用倒装芯片贴装工艺,并通过回流焊对芯片进行焊接。

随后采用模具工艺封装组装好的芯片,并作为模具底部填充材料。采用激光脱粘技术将玻璃RDL支撑与封装分离。最后,使用机械刀片切割技术将各个封装分离。

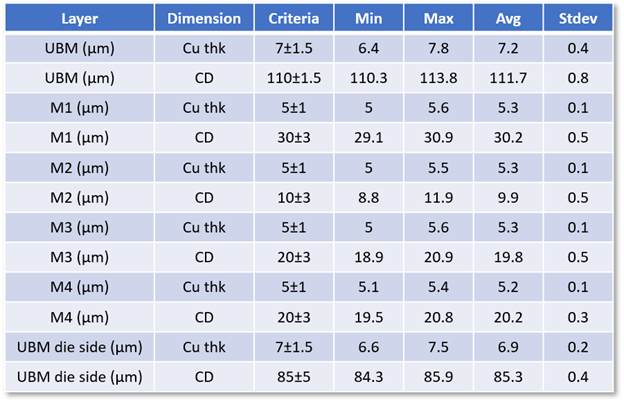

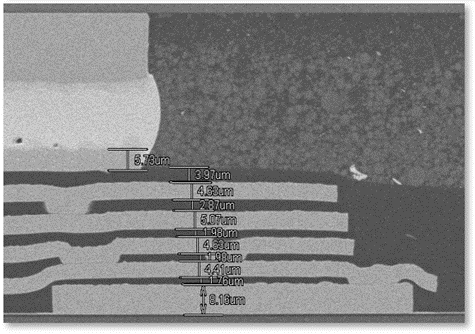

重分布层的最小临界尺寸为 5µm 线距和 5µm 线宽。UBM 层的标称厚度为 7µm,所有 4个重分布层的标称厚度均为 5µm,介电层的厚度为 5µm。与 RDL 金属层相关的在线测量数据如表 1 所示,所有值均符合规定的规格。

表1:金属层相关数据

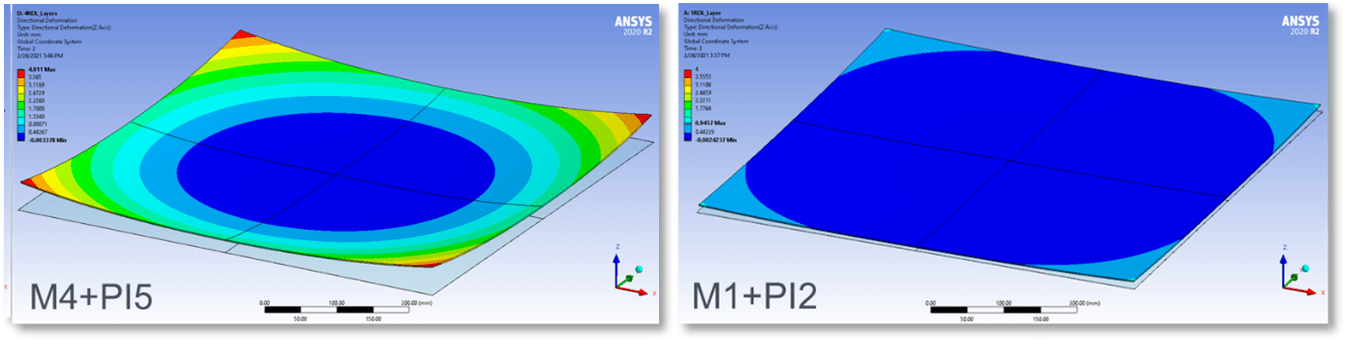

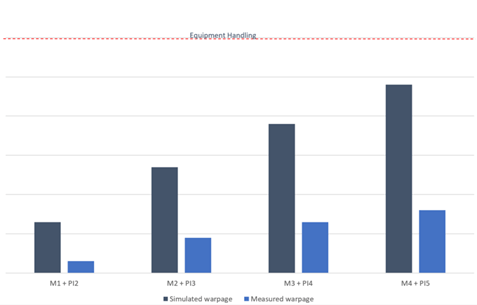

对于采用多层RDL的大尺寸面板,一个值得关注的问题是由于不同介电层的固化以及玻璃与介电层之间CTE不匹配而导致的翘曲。在开始操作之前,进行了有限元模拟以评估预期的翘曲。模拟的堆叠结构为四层RDL层和五层介电层。三种玻璃具有三种不同的CTE,范围从与硅(Si)良好匹配的CTE、与芯片优先扇出型良好匹配的CTE,到中间CTE值。根据CTE,考虑了两种面板厚度。

图 7:1L RDL 和 4L RDL 后的面板翘曲

正如预期的那样,模拟表明,随着额外的 RDL(金属+电介质)的出现,翘曲效应会累积。

图 8:基于两种面板厚度和三种 CTE 的面板翘曲

模拟翘曲量与实测翘曲量在趋势上吻合良好,但观察到的翘曲量明显低于模拟预测值,且与图表所示的设备操作规格相差甚远。介电膜的不连续性很可能是造成这种差异的原因。

完成后续组装步骤后,进行机械横截面分析,以分析与标称值相比的层结构,并作为封装完整性的初步评估。

图 9:0 小时时测量的横截面层厚度

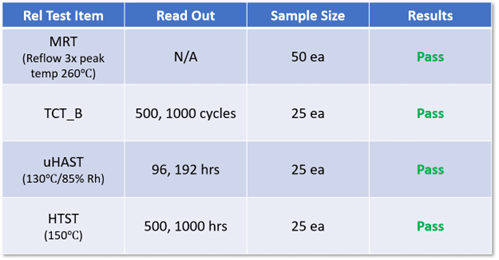

对单片单元进行了一系列可靠性测试。本次可靠性评估主要关注层间附着力和封装完整性。可靠性测试结果如表2所示。所有测试结果均为阳性,应力测试后未观察到任何故障。

表 2:组件级可靠性结果

结论

本文介绍了一种新颖的面板级封装技术平台。该平台在先芯片和后芯片配置的WLCSP、WLFO和PLFO设计中均具有出色的灵活性。多层后芯片测试平台的结果显示,其可靠性极佳,且物料清单与等效晶圆级封装相同。成本建模结果也表明,该技术可实现显著的效益提升。

仿真提出的多层RDL结构翘曲问题并未通过在线数据得到证实——数据显示存在显著的处理裕度。可靠性评估证明了采用650 mm x 650 mm面板格式加工的后芯片封装的完整性。

艾邦建有玻璃基板与TGV技术交流群,可以加强产业链的合作,促成各企业的需求对接,同时您也可以与行业精英共同探讨玻璃基板及TGV技术的前沿动态,共享资源,交流经验,欢迎您的加入。

加微信李小姐:18823755657(同微信)

邮箱:lirongrong@aibang.com

扫码添加微信,咨询会议详情

注意:每位参会者均需要提供信息

方式二:长按二维码扫码在线登记报名

或者复制网址到浏览器后,微信注册报名

https://www.aibang360.com/m/100255?ref=172672