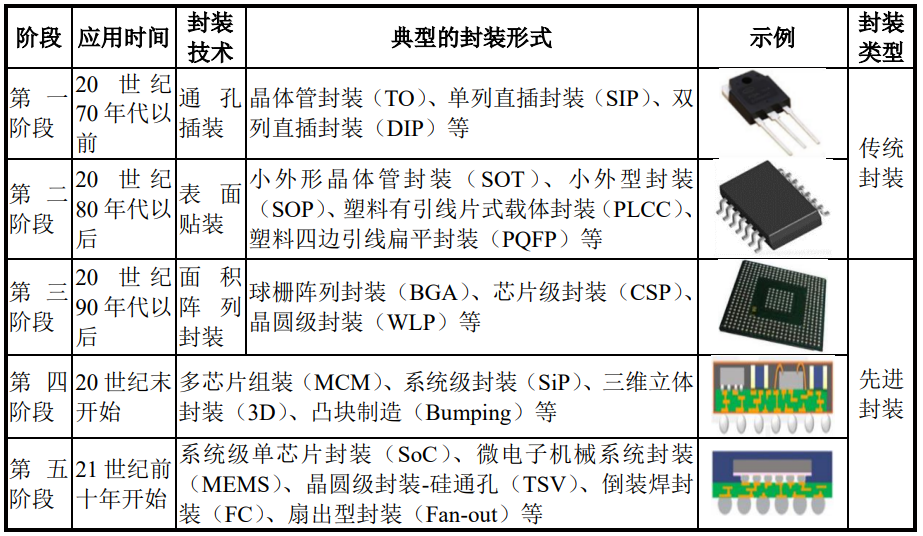

本文将介绍目前全球半导体封装技术主要经历的五个发展阶段,如有遗漏或错误,欢迎留言补充或加入艾邦半导体材料交流群进行讨论。

第一阶段:1950-1970年代:直插式封装时代

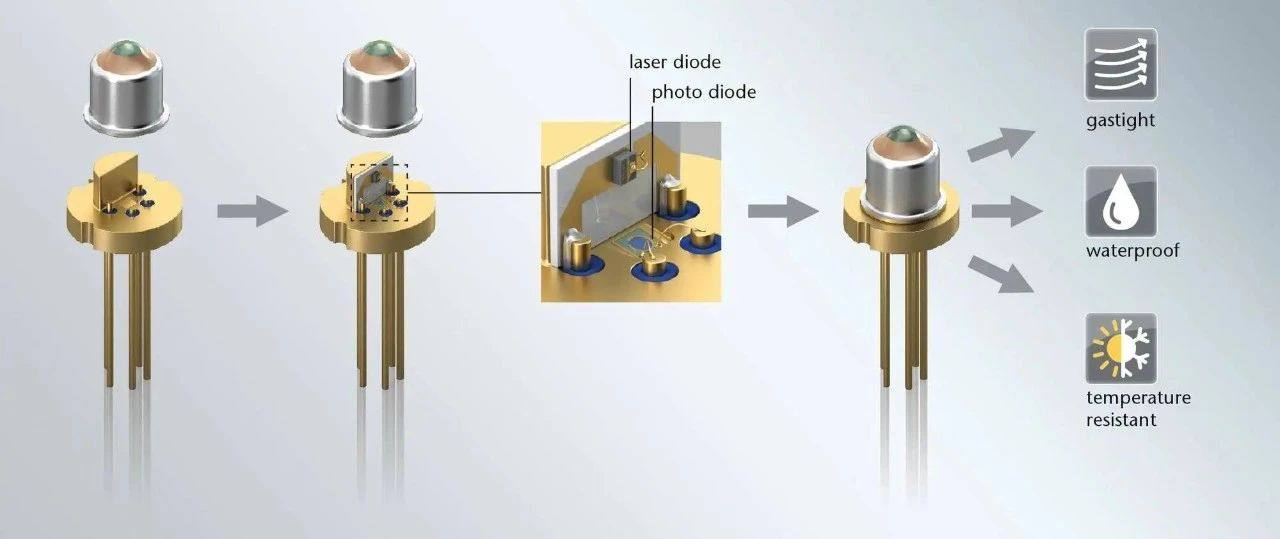

1.晶体管封装(TO封装):首款金属圆壳封装,三根引脚从底部伸出,具备良好的机械强度和密封性,但体积大、引脚数有限。应用于早期分立晶体管和低集成度集成电路。

晶体管封装(TO封装)

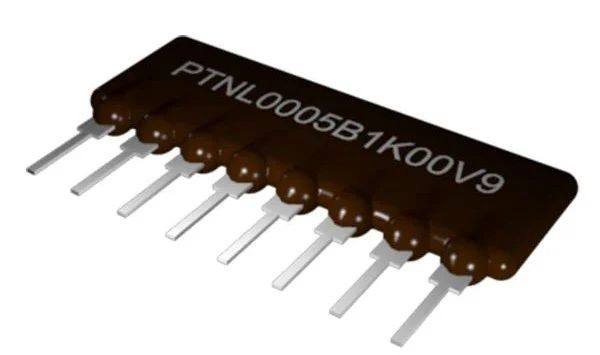

2.单列直插封装(SIP封装):所有引脚排成单列,引脚间距(Pitch)通常为标准值,如 2.54 mm 或 1.27 mm,需要插入印刷电路板(PCB)的金属化通孔中进行焊接。

单列直插封装(SIP封装)

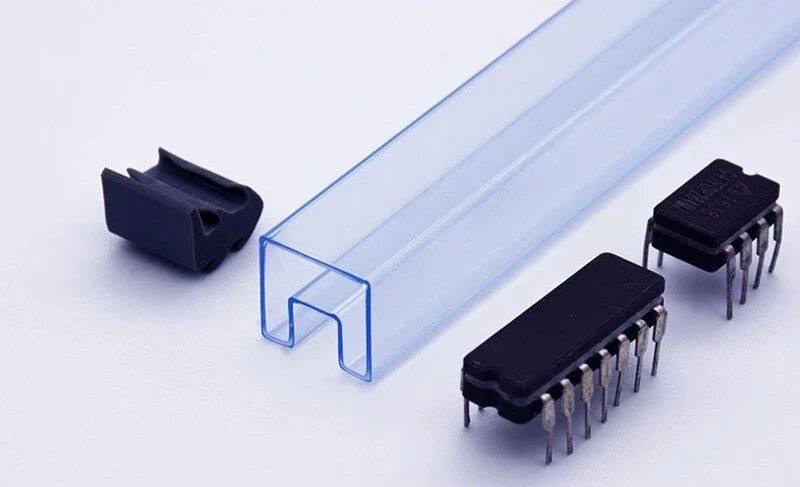

3.双列直插封装(DIP封装):1960年代双列直插式封装诞生,采用塑料材料替代金属,引脚双列排布,数量可达64根。成本低、易于插拔,成为早期微处理器(如Intel 8086)和存储芯片的标准封装。

双列直插封装(DIP封装)

第二阶段:表面贴装技术(1980s)

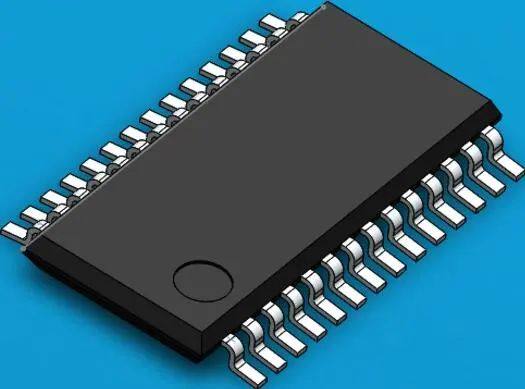

SOP封装

SOP封装

第三阶段:1990s后阵列封装的兴起

-

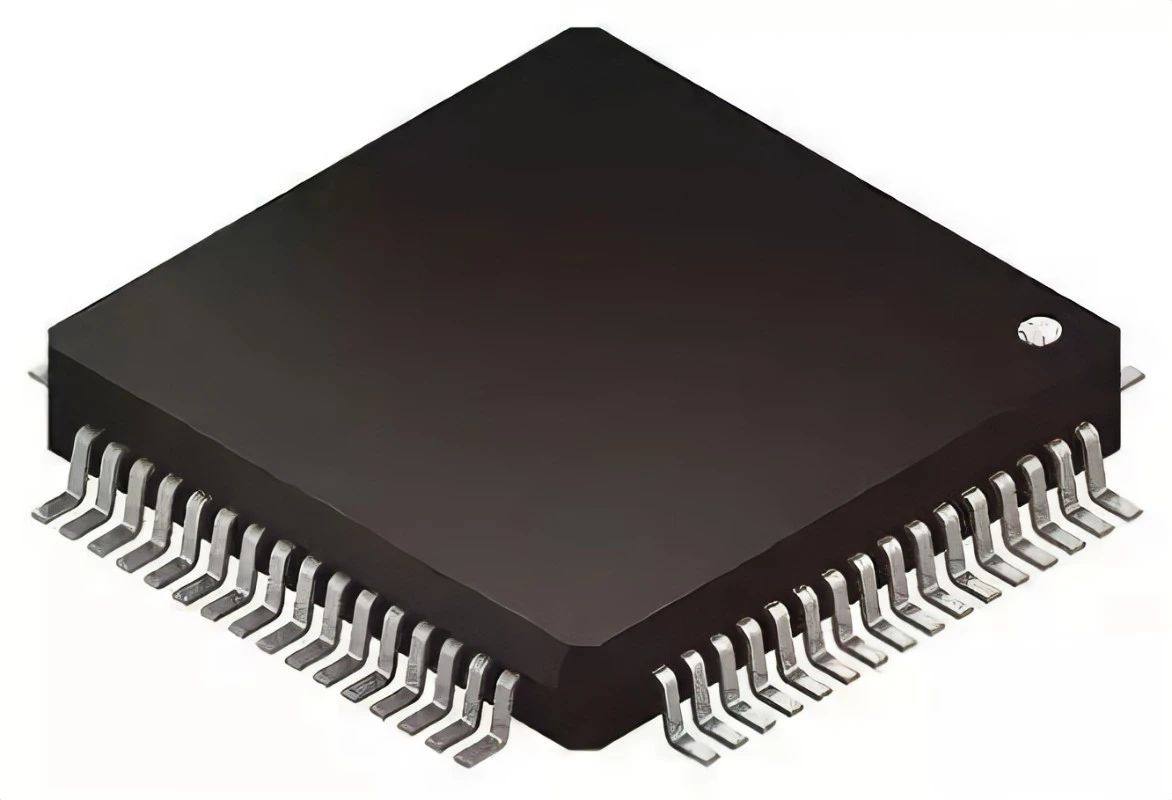

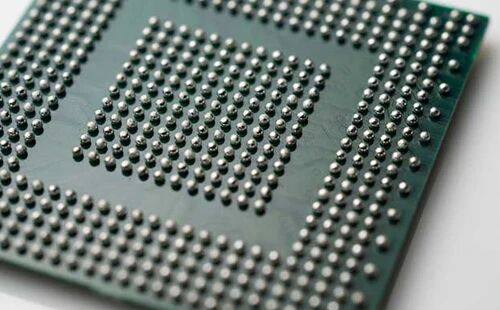

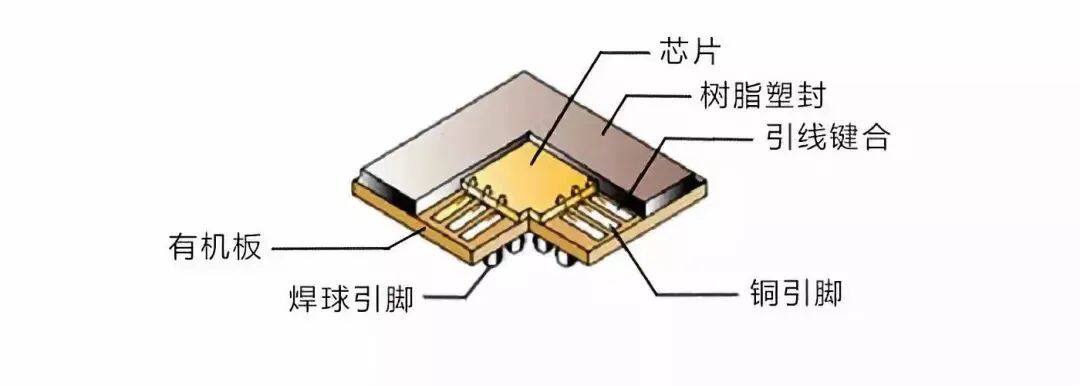

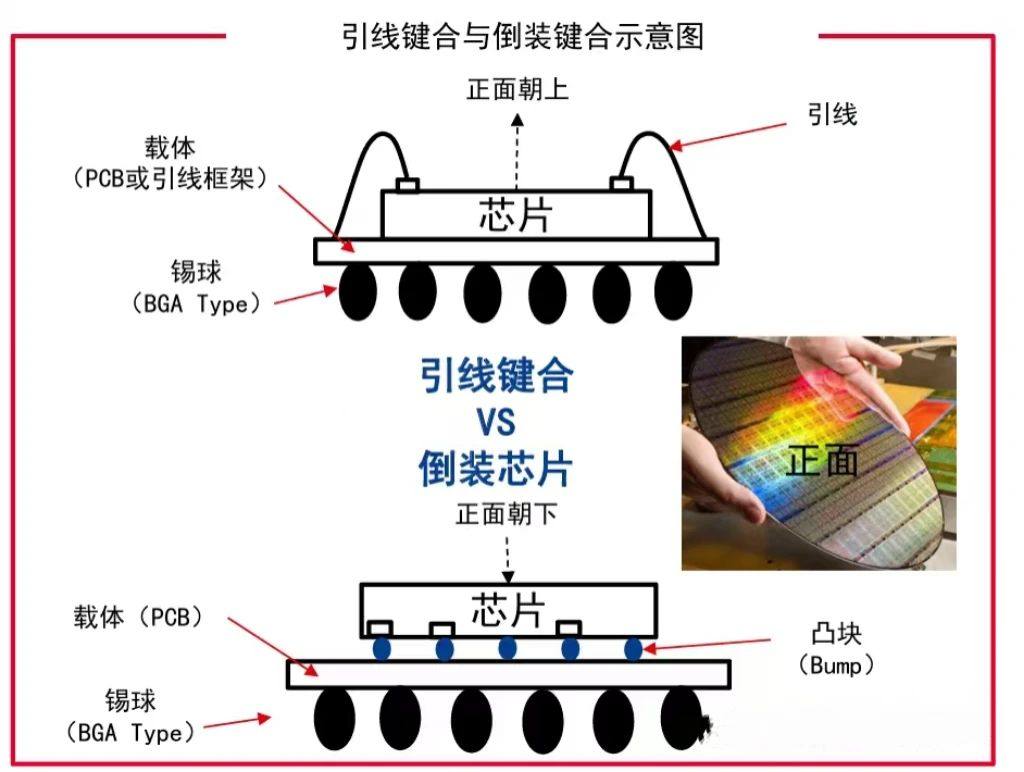

BGA封装(Ball Grid Array):球栅阵列封装底部以阵列形式排列的锡球作为引脚,通过回流焊工艺将这些锡球与印刷电路板(PCB)上的焊盘连接。

相比传统的QFP(四侧引脚扁平封装),BGA的引脚间距(Pitch)可以做得更小,从而实现I/O数量突破1000+,散热能力提升50%。

塑封BGA(PBGA)

塑封BGA(PBGA)

PBGA制作成本低,性价比高,焊球参与再流焊点形成,共面度要求宽松。与环氧树脂基板热匹配性好,装配至PCB时质量高,性能好。

-

CSP封装(Chip Scale Package):CSP芯片级封装是BGA封装技术下的突破,要求封装的尺寸不超过芯片本身尺寸的1.2倍。

为了实现这个极小的尺寸目标,CSP通常采用微小的焊球和更精细的布线技术,因此从外观上看,它非常像一个小型的、更精致的BGA,不仅减小了封装尺寸,还提高了集成度。

|

|

|

|

|---|---|---|

| 核心定义 |

|

|

| 尺寸与面积 |

|

|

| 应用场景 |

|

|

| 与芯片关系 |

|

|

第四阶段:20世纪末微系统封装的形式出现

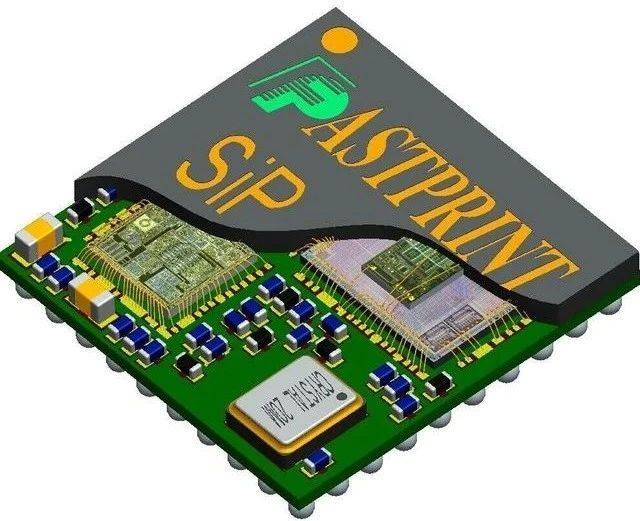

随着电子信息技术的发展,人们对电子产品小型化,功能化,高集成,环保型等方向需求的不断增大,作为集成电路元器件保护和接口的微电子封装扮演着越来越重要角色,由此产生了许多新技术,新材料和新设计。

实现微小型化的关键与基础是适应电子整机与系统需要的微电子封装与组装技术的不断进步。其中基于芯片系统级或者是片上系统集成SoC(System on Chip)、芯片级组件互联MCM(Multi-Chip Module)、系统级封装 SiP(System in Package)、板级别的SOP(System on Package)等技术对这一领域的发展起到了十分重要的作用。

系统级封装 SiP

系统级封装 SiP

第五阶段先进封装纪元(21世纪至今)

就技术成熟度而言,目前全球半导体封装的主流技术处于第三阶段(球栅阵列封装),并逐步向第四阶段和第五阶段的封装技术迈进。

近年来国内领先封装企业通过自主研发和收购兼并等方式逐步掌握了部分先进封装技术,但仍以第一、第二阶段的传统封装技术为主流, 国内封装行业整体发展水平与境外仍存在一定差距。

由于先进封装技术工艺革新难点多、成本高,国内较大规模广泛应用仍需较长时间。

塑料在半导体制程中发挥重要作用,抗静电塑料、PP、ABS、PC、PPS、PEI,氟材料、PEEK、PI、PAI等塑料被广泛应用半导体制程中,如载具,治具,洁净室,管道,输送系统,化学品存放等。为了加快上下游交流艾邦建有半导体产业链微信群,欢迎加入产业链微信群。

|

序号 |

拟定议题 |

演讲单位 |

|

1 |

PEEK材料在半导体不同制程中的应用 |

邀请中 |

|

2 |

PPS材料在半导体领域的应用 |

邀请中 |

|

3 |

半导体级PP材料应用与研究 |

邀请中 |

|

4 |

特种工程塑料型材在半导体设备领域应用 |

邀请中 |

|

5 |

氟塑料在酸碱制程中的耐腐蚀性能极限测试方法论 |

邀请中 |

|

6 |

半导体级氟塑料国产化进展 |

邀请中 |

|

7 |

半导体级氟塑料(PFA)管材挤出工艺 |

邀请中 |

|

8 |

氟橡胶在半导体设备密封领域的应用 |

邀请中 |

|

9 |

高性能橡胶在半导体制造热管理中的创新应用:耐高温密封与高效散热技术 |

邀请中 |

|

10 |

半导体晶圆传输系统橡胶缓冲材料的抗损伤与抗静电协同优化技术 |

邀请中 |

|

11 |

塑料晶圆载具中的应用 |

邀请中 |

|

12 |

IC托盘材料选型 |

邀请中 |

|

13 |

CMP保持环材料耐磨性提升 |

邀请中 |

|

14 |

晶圆清洗花篮的材料介绍 |

邀请中 |

|

15 |

先进封装光罩盒的新需求 |

邀请中 |

|

16 |

半导体微污染控制:析出物检测与工艺适配 |

邀请中 |

|

17 |

抗静电ABS在半导体制程中的应用 |

邀请中 |

|

18 |

抗静电PC/PVC洁净室板材表面处理技术 |

邀请中 |

|

19 |

全球PFAS法规收紧对含氟高分子供应链的影响与替代材料开发进展 |

邀请中 |

|

20 |

终端对半导体材料的需求及应用趋势 |

邀请中 |

更多议题征集中,创新演讲及赞助请联系Mickey周小姐: 18320865613(同微信)

报名方式一:加微信并发名片报名

电话:艾果儿 18312560351(同微信)

邮箱:ab008@aibang.com

扫码添加微信,咨询会议详情

注意:每位参会者均需要提供信息

报名方式二:长按二维码扫码在线登记报名

或者复制网址到浏览器后,微信注册报名:

https://www.aibang360.com/m/100258?ref=172672

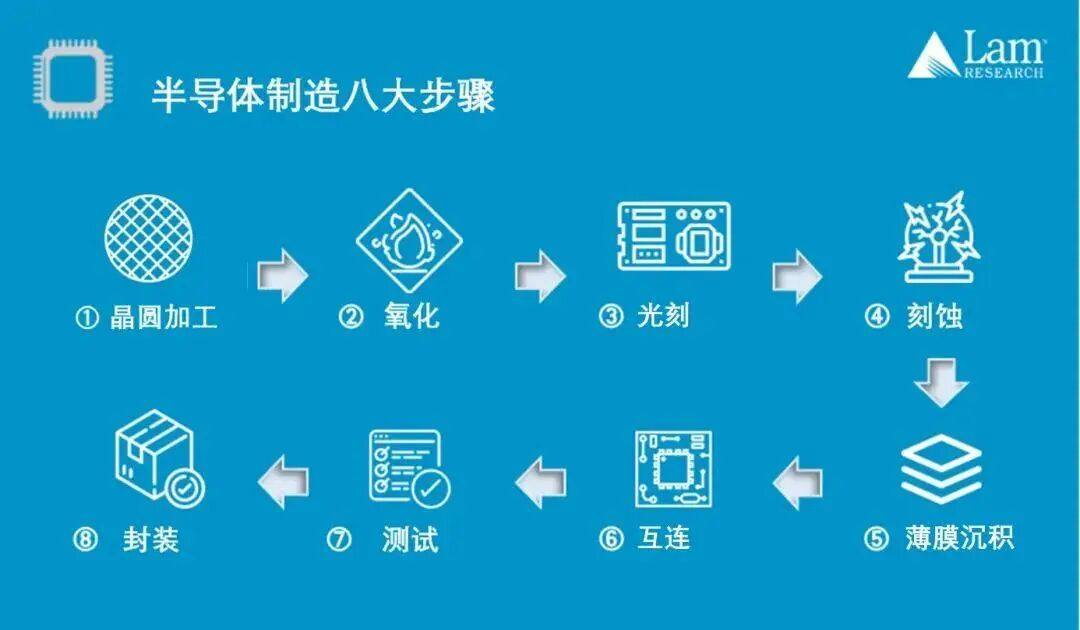

一颗芯片的制造工艺非常复杂,需经过几千道工序,加工的每个阶段都面临难点。欢迎加入艾邦半导体产业微信群:

长按识别二维码关注公众号,点击下方菜单栏左侧“微信群”,申请加入群聊